### CHAPTER 4

### SYM-1 SYSTEM OVERVIEW

This chapter will describe your SYM-1 microcomputer system's hardware and software in sufficient detail to allow you to understand its theory of operation. Each integrated circuit (IC) component on the SYM-1 board is discussed and related to a functional block diagram. Each functional module is then discussed schematically and the I/O connectors are described. The system memory is then covered and the software is discussed briefly. Detailed data on the software itself is found in Chapter 5 of this manual.

### 4.1 HARDWARE DESCRIPTION

The SYM-1 microcomputer consists primarily of a 6502 CPU, one or more 6522 Versatile Interface Adapters (VIA), a 6532 Memory and I/O Controller and two types of memory involving any combination of several different components. Because of the flexibility of the memory structure, it is discussed in a separate section (4.2, below).

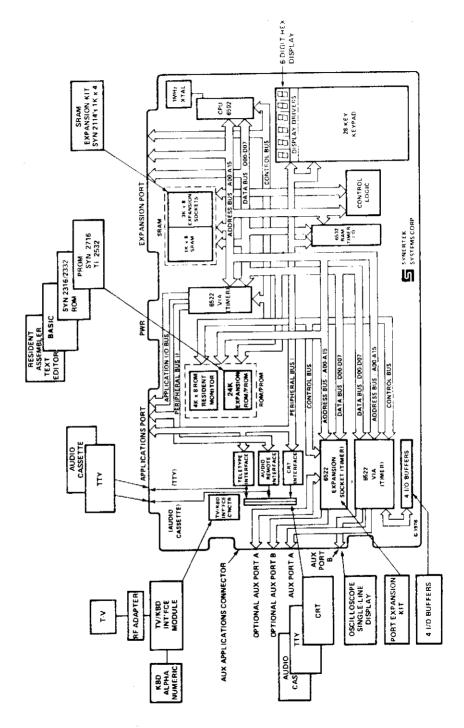

In any microcomputer system, all the components work together functionally as well as being physically interconnected. These connections are illustrated in Figure 4-1, a block diagram of the SYM-1 microcomputer system.

### 4.1.1 6502 CPU Description

The Central Processing Unit (CPU) of the SYM-1 microcomputer system is the 6502 microprocessor which is designed around a basic two-bus architecture--one full 16-bit address bus and an eight-bit data bus. Two types of interrupts are also available on the processor. Packaged in a 40-pin dual-in-line package, the 6502 offers a built-in oscillator and clock drivers. Additionally, the 6502 provides a synchronization signal which indicates when the processor is fetching an instruction (operation code) from program memory.

During the following discussion of the 6502, you should refer to the Data Sheets in this manual, which describe the pin connections for all three of the major types of devices present on the SYM-1 microprocessor system.

4.1.1.1 <u>Bus Structure</u>. The 6502 CPU is organized around two main busses, each of which consists of a separate set of parallel paths which can be used to transfer binary information between the components and devices in the SYM-1 system. The address bus transfers the address generated by the processor to the address inputs of the peripheral interface and memory devices (i.e., the 6522 and 6532 components). Note that in the Data Sheet for the 6502, the address lines originate at pins 9-20 and 22-25 of the 6502 CPU. These address lines go to pins 2-17 on the 6522 and/or to pins 2, 5-8, 10-15 and 34-40 on the 6532. Since the processor is almost always the only source of address generation in a system, an address bus is generally referred to as "unidirectional." That is the case with the SYM-1 microcomputer system. Since the address bus consists of 16 lines, the processor may read and write to a total of 65,536 bytes of storage (i.e., program memory words, RAM words, stack, I/O devices and other information), a condition which is normally referred to as a "64K memory capacity."

4-1. FUNCTIONAL BLOCK DIAGRAM

The other bus in the 6502 processor is called the data bus. It is an eight-bit bidirectional data path between the processor and the memory and interface devices. When data is moved from the processor to a memory location, the system performs a write; when the data is traveling from memory to the CPU, a read is being performed. Pins 26-33 on the 6502, 6522 and 6532 devices are all data lines connected to the data bus. The direction of the transfer of data between these pin connectors is determined by the output of the Read/Write (R/W, Pin 34) of the 6502. This line enables a write memory when it is "low" (when its voltage is below 0.4 VDC). Write is disabled and all data transfers will take place from memory to the CPU if the level is high (greater than 2.4 VDC).

One of the important aspects of the 6502 CPU is that it has two interrupt input lines available, Interrupt Request (labeled  $\overline{IRQ}$  in the Data Sheet) and a Non-Maskable Interrupt (labelled  $\overline{NMI}$ ).

Interrupt handling is one of the key aspects of microprocessor system design. Although the idea of interrupt handling is fairly simple, a complicating factor is the necessity for the processor to be able to handle multiple interrupts in order of priority (usually determined by the programmer) and not "losing track" of any of them in the process. These are concepts which you as a programmer-user of the SYM-1 will be concerned with only in advanced applications. The handling of user-generated interrupts is discussed elsewhere in this manual. If you do have occasion to alter pre-determined interrupt handling, it will be helpful for you to understand how the process works for the two types of interrupts in the 6502.

There are two main differences between the  $\overline{IRQ}$  and  $\overline{NMI}$  signals and their handling. First,  $\overline{IRQ}$  will interrupt the CPU only if a specific flag-the Interrupt Disable Flag (I)—in the system's Processor Status Register is cleared, i.e., zero. If this flag is "set"—i.e., one—the  $\overline{IRQ}$  is disabled until the flag is cleared. But an  $\overline{NMI}$  request (as its name implies) always causes an interrupt, regardless of the status of the I-flag. The other main difference between the two types of interrupts is that the  $\overline{IRQ}$  interrupt is "level sensitive." Any time the signal is less than 0.4 VDC and the Interrupt Disable flag is cleared, an interrupt will take place. In the case of  $\overline{NMI}$ , the interrupt is said to be "edge-sensitive" because it is dependent on a sequence of timing events. This interrupt will occur only if the signal goes "high" (i.e., exceeds 2.4 VDC) and then goes back to ground (less than 0.4 VDC). The interrupt occurs on the negative-going transition past 0.4 V.

The Data Sheet contains a summary of the 40 pins on the 6502 CPU and their function. Note that three of the pins--5, 35 and 36--are not connected on the 6502.

4.1.1.2 <u>Summary</u>. The 6502 CPU is a versatile processor. It was selected for your SYM-1 microprocessor system because of its overall functional characteristics, which facilitate its use in a wide variety of applications. Its role in the SYM-1 system will become clearer when we discuss programming and software in Section 4.3 and in Chapters 5 and 6.

### 4.1.2 6522 Description

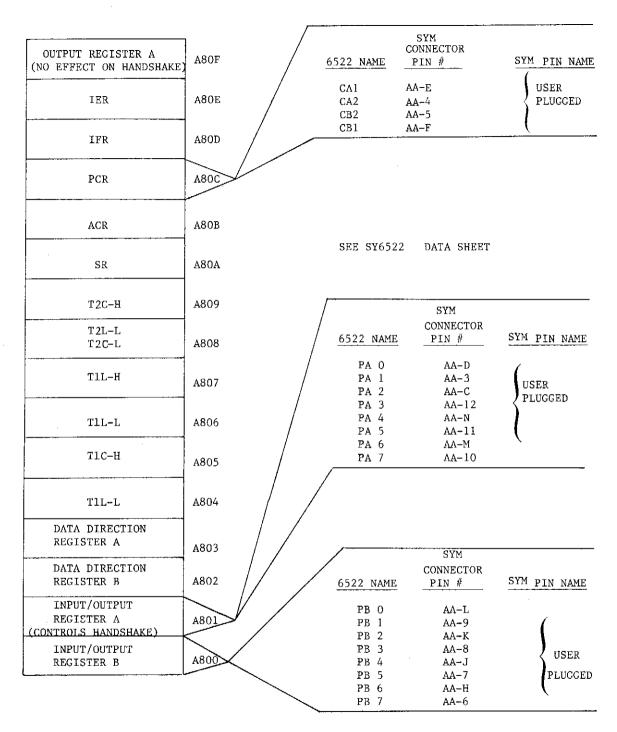

The SY6522 Versatile Interface Adapter (VIA) is a highly flexible component used on the SYM-I module to handle peripheral interfaces. Two of these devices are standard components on your SYM-I; a third may be added merely by plugging it into the socket (U28) provided. Control of the peripheral devices is handled primarily through the two eight-bit bi-directional ports. Each line of these ports can be programmed to act as

The other bus in the 6502 processor is called the data bus. It is an eight-bit bidirectional data path between the processor and the memory and interface devices. When data is moved from the processor to a memory location, the system performs a write; when the data is traveling from memory to the CPU, a read is being performed. Pins 26-33 on the 6502, 6522 and 6532 devices are all data lines connected to the data bus. The direction of the transfer of data between these pin connectors is determined by the output of the Read/Write (R/W, Pin 34) of the 6502. This line enables a write memory when it is "low" (when its voltage is below 0.4 VDC). Write is disabled and all data transfers will take place from memory to the CPU if the level is high (greater than 2.4 VDC).

One of the important aspects of the 6502 CPU is that it has two interrupt input lines available, Interrupt Request (labeled  $\overline{IRQ}$  in the Data Sheet) and a Non-Maskable Interrupt (labelled  $\overline{NMI}$ ).

Interrupt handling is one of the key aspects of microprocessor system design. Although the idea of interrupt handling is fairly simple, a complicating factor is the necessity for the processor to be able to handle multiple interrupts in order of priority (usually determined by the programmer) and not "losing track" of any of them in the process. These are concepts which you as a programmer-user of the SYM-1 will be concerned with only in advanced applications. The handling of user-generated interrupts is discussed elsewhere in this manual. If you do have occasion to alter pre-determined interrupt handling, it will be helpful for you to understand how the process works for the two types of interrupts in the 6502.

There are two main differences between the  $\overline{\rm IRQ}$  and  $\overline{\rm NMI}$  signals and their handling. First,  $\overline{\rm IRQ}$  will interrupt the CPU only if a specific flag—the Interrupt Disable Flag (I)—in the system's Processor Status Register is cleared, i.e., zero. If this flag is "set"—i.e., one—the  $\overline{\rm IRQ}$  is disabled until the flag is cleared. But an  $\overline{\rm NMI}$  request (as its name implies) always causes an interrupt, regardless of the status of the I-flag. The other main difference between the two types of interrupts is that the  $\overline{\rm IRQ}$  interrupt is "level sensitive." Any time the signal is less than 0.4 VDC and the Interrupt Disable flag is cleared, an interrupt will take place. In the case of  $\overline{\rm NMI}$ , the interrupt is said to be "edge-sensitive" because it is dependent on a sequence of timing events. This interrupt will occur only if the signal goes "high" (i.e., exceeds 2.4 VDC) and then goes back to ground (less than 0.4 VDC). The interrupt occurs on the negative-going transition past 0.4 V.

The Data Sheet contains a summary of the 40 pins on the 6502 CPU and their function. Note that three of the pins--5, 35 and 36--are not connected on the 6502.

4.1.1.2 <u>Summary</u>. The 6502 CPU is a versatile processor. It was selected for your SYM-1 microprocessor system because of its overall functional characteristics, which facilitate its use in a wide variety of applications. Its role in the SYM-1 system will become clearer when we discuss programming and software in Section 4.3 and in Chapters 5 and 6.

### 4.1.2 6522 Description

The SY6522 Versatile Interface Adapter (VIA) is a highly flexible component used on the SYM-I module to handle peripheral interfaces. Two of these devices are standard components on your SYM-I; a third may be added merely by plugging it into the socket (U28) provided. Control of the peripheral devices is handled primarily through the two eight-bit bi-directional ports. Each line of these ports can be programmed to act as

either an input or an output. Also, several of the peripheral I/O lines can be controlled directly from the two very powerful interval timers integrated into the chip. This results in the capability to 1) generate programmable frequencies, 2) count externally generated pulses, and 3) to time and monitor real time events.

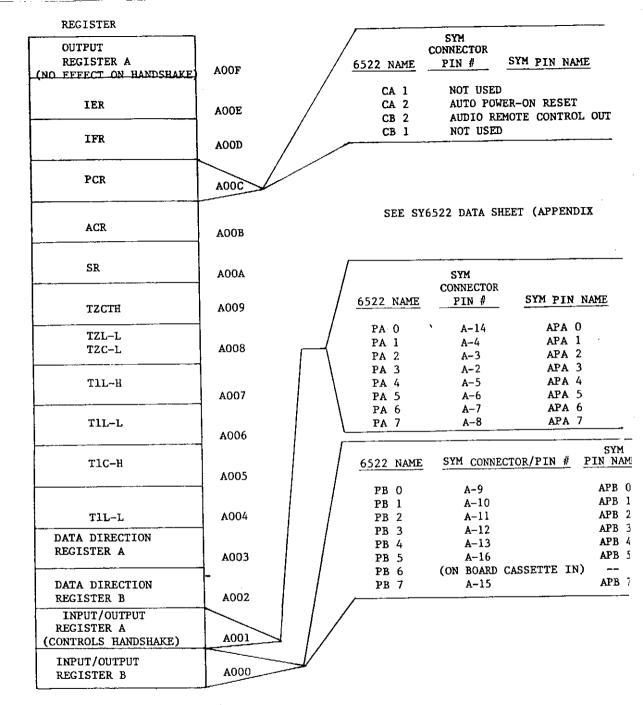

A description of the pin designations on the SY6522 is contained in the Data Sheet enclosed with your SYM-1. It should be used in following the discussion of the operation of the component in the SYM-1 module which follows. The Memory Map of the SYM-1 module (Figure 4-10) will also be helpful during this discussion.

4.1.2.1 Processor Interface. Data transfers between the SY6522 and the CPU (6502) take place over the eight-bit data bus (DB0-DB7) only while the Phase Two Clock (02) is high and the chip is selected (i.e., when CS1 is high and CS2 is low). The direction of these data transfers is controlled by the Read/Write line (R/W). When this line is low, data will be transferred out of the processor into the selected 6522 register; when R/W is high and the chip is selected, data will be transferred out of the SY6522. The former operation is described as the write operation, the latter the read operation.

Four Register Select lines (RSO-RS3) are connected to the processor's address bus to allow the processor to select the internal SY6522 register which is to be accessed. There are 16 possible combinations of these four bits and each combination accesses a specific register. Because of the fact that the SY6522 is a programmable-addressable device, these RS line settings, in combination with the basic device address, form the specific register address shown in the 6522 Data Sheet.

Two other lines are used in the SY6522 interface to the 6502 processor. The Reset line ( $\overline{RES}$ ) clears all internal registers to a logical zero state (except T1, T2 and SR), placing all peripheral lines in the input state. It also disables the timers, shift register and other on-chip functions and disables interrupting from the chip. The Interrupt Request line ( $\overline{IRQ}$ ) generates a potential interrupt to the CPU when an internal interrupt flag is set and a corresponding interrupt enable bit is set to a logical "1." The resulting output signal is then "wire or'ed" with other similar signals in the system to determine when and whether to interrupt the processor.

4.1.2.2 Peripheral Interface. As we mentioned earlier, peripheral interface is handled largely over two eight-bit ports, with each of the 16 lines individually programmable to act as an input or output line. Port A consists of lines PAO-PA7 and Port B of lines PBO-PB7.

Three registers are used to access each of the eight-bit peripheral ports. Each port has a Data Direction Register (DDRA and DDRB), which is used in specifying whether the pins are to act as inputs or outputs. If a particular bit in the Data Direction Register is set to zero, the corresponding peripheral pin is acting as an input; if it is set to "I," the pin acts as an output point.

Each of the 16 peripheral pins is also controlled by a bit in the output register (ORA and ORB) and a similar bit in the Input Register (IRA and IRB). When the pin is programmed to act as an output, the voltage on the pin is controlled by the corresponding bit in the Output Register. A "I" in the appropriate Output Register causes the pin to go "high" (2.4 VDC or higher), and a zero causes it to go "low (0.4 VDC or lower).

Functionally, reading a peripheral port causes the contents of the appropriate Input Register to be transferred to the Data Bus.

The SY6522 has a number of sophisticated features which allow very positive control of data transfers between the processor and peripheral devices through the operation of "handshake" lines which involve the use of Peripheral Control Lines (CA1-CA2 and CB1-CB2). These operations are beyond the scope of this manual; if you are interested in further information, you should consult the data sheet enclosed.

### 4.1.3 6532 Description

Like the SY6522 described above, the SY6532 is used on the SYM-1 module to control peripheral interface. Only one SY6532 is furnished with your SYM-1 and no others are provided for.

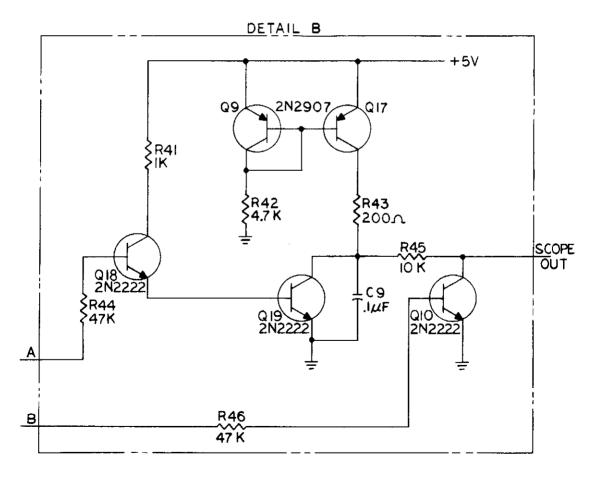

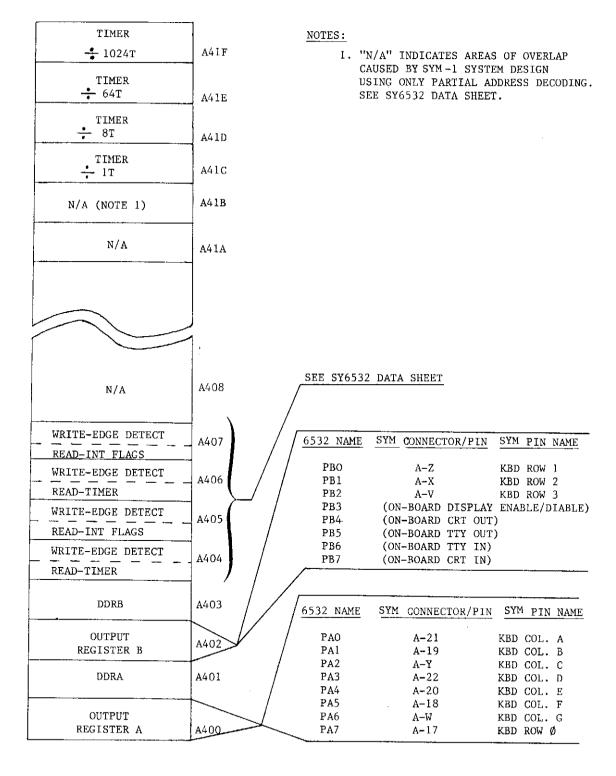

From an operational standpoint, the SY6532 is quite similar to the SY6522. One key difference, particularly on your SYM-I module, is the presence of a 128-byte x 8-bit RAM within the SY6532. This is the location referred to as "System RAM" in discussions of the software operation and in the Memory Map (Figure 4-10).

A description of the pin designations on the SY6532 is included in the enclosed Data Sheet. You will notice that, like the SY6522, the SY6532 contains 16 peripheral I/O pins divided into two eight-bit ports (lines PA0-PA7 and PB0-PB7). Each of these pins can be individually programmed to function in input or output mode.  $\overline{\text{IRQ}}$  on the SYM-1 SY6532 is not connected.

The Address lines (A0-A6) are used with the RAM Select ( $\overline{RS}$ ) line and the Chip Select lines (CS1 and  $\overline{CS2}$ ) to address the SY6532. It is in this addressing that the SY6532 differs somewhat from the SY6522's on your SYM-I module. To address the 128-byte RAM on the SY6532, CS1 must be high and  $\overline{CS2}$  and  $\overline{RS}$  must both be low. To address the I/O lines and the self-contained interval timer, CS1 and  $\overline{RS}$  must be high and  $\overline{CS2}$  must be low. In other words, CS1 is high and  $\overline{CS2}$  is low to address the chip;  $\overline{RS}$  is used to differentiate between addressing RAM and the I/O Interval Timer functions. Distinguishing between I/O lines and the Interval Timer is the function of Address Line 2 (A2), which is high to address the timer and low to address the I/O section. Again, the Memory Map in Figure 4-10 clarifies these operations since they are largely software-directed and address-dependent.

### 4.1.4 Functional Schematics

Understanding the electrical interfaces among the various components may be of some interest to you as you use and expand your SYM-1 microcomputer. The figures on the following pages include segmented schematics, where each figure provides an electronic overview of the interface between the CPU and its related component devices and peripherals.

Table 4-I describes the contents of each figure in this group of schematic segments.

Table 4-1. INDEX OF SCHEMATIC SEGMENTS FIGURES 4-2 TO 4-9

| Figure     | Function/Segment Diagrammed   |

|------------|-------------------------------|

| * *8***    |                               |

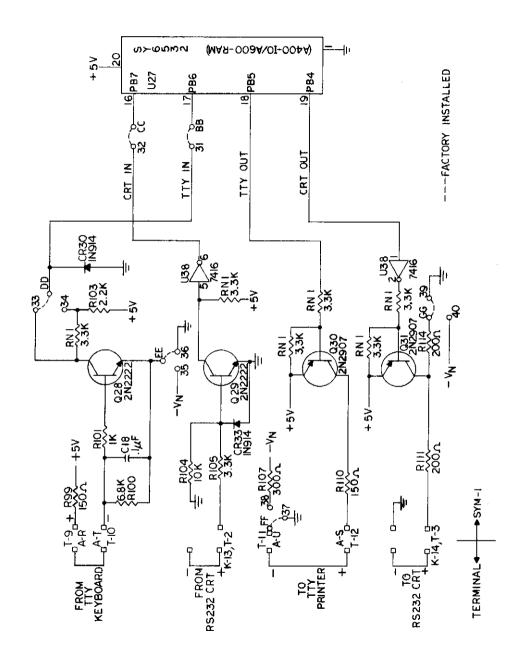

| 4-2        | TTY and CRT Interface         |

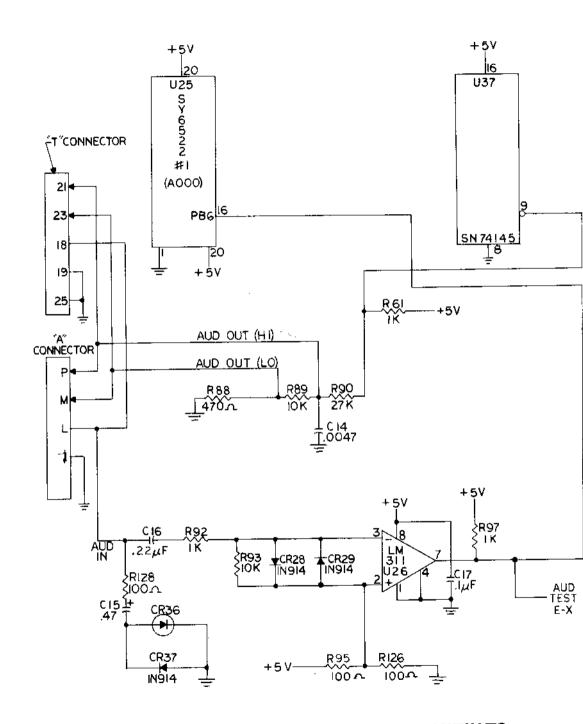

| 4-3        | Audio Cassette Interface      |

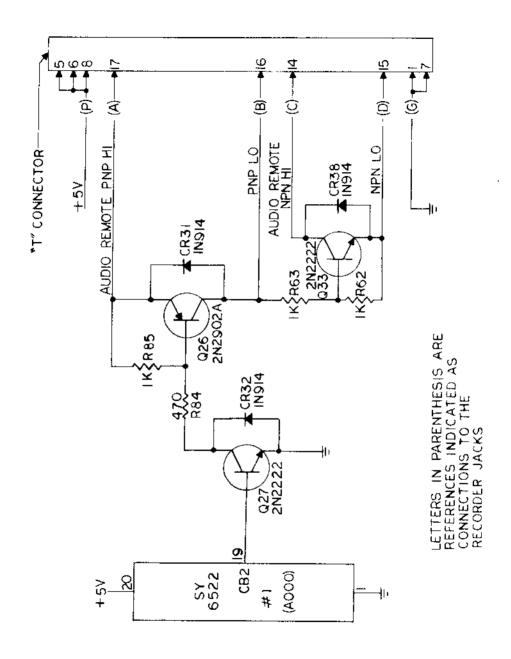

| 4-4        | Audio Cassette Remote Control |

| 4-5        | I/O Buffer                    |

| 4_6        | Keyboard/Display              |

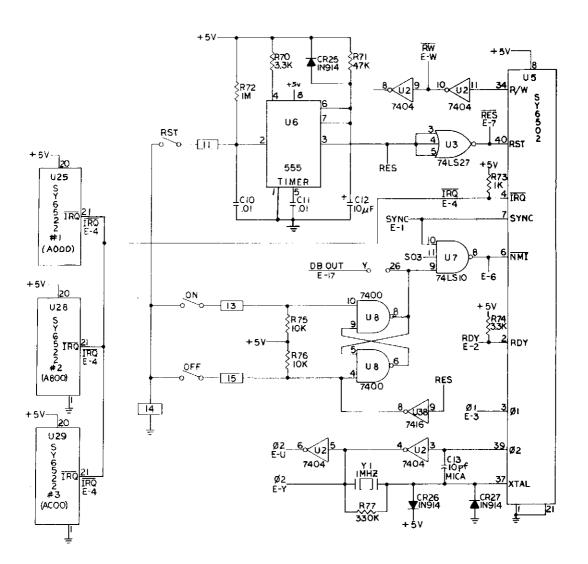

| 4-6<br>4-7 | Control Section               |

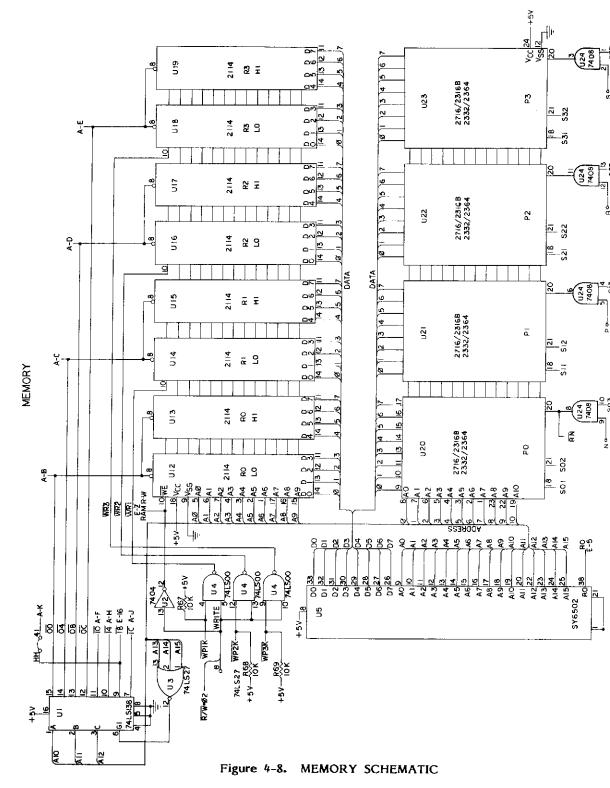

| 4-8        | Memory Section                |

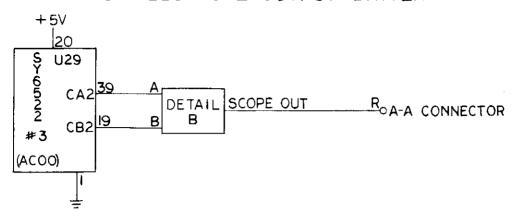

| 4-9        | Oscilloscope Output Driver    |

Table 4-2 provides, in summary form, a list of the connector points on the four SYM-1 connectors. This allows you to determine pin and connector configurations for various application options.

CONNECTOR POINTS AND THEIR FUNCTIONS IN SYM-1 Table 4−2.

9 10 11 12 13 14 15 16 17 18 19 20 21 22 Component Side K L M N P R S T U V W X Y Z Solder Side 7 H J 5 E F 3 4 C D 1 2 A B Key:

| N (AA)                     | +5V  | 5    | )<br>+ ( ) | 2 PA 2  | 2 PA 0     | 2 CA 1 | 2 CB 1                                        | 2 CD 1     | 2 1 1 2 2 2 2 3 3 3 3 3 3 3 3 3 3 3 3 3 | 2 FD 6      | 7 HB 7   | 2 PB 0      | 2 PA 6         | 2 DA 4    | 7 7 7          | 7 7 7          | SCOPE          | 3 PB 3      | 3 PR 1         | 3 PA 7      | 3 DA 0    | 7 7 7 7  |            | 3 PA 2   | 3 PB 4         | 3 PB 6     | <br> - |

|----------------------------|------|------|------------|---------|------------|--------|-----------------------------------------------|------------|-----------------------------------------|-------------|----------|-------------|----------------|-----------|----------------|----------------|----------------|-------------|----------------|-------------|-----------|----------|------------|----------|----------------|------------|--------|

| LICATIC                    | V    | ; a  | <b>a</b> ( | ١       | Ω          | ш      | Įī                                            | . ;        | ; -                                     | <b>~</b> \$ | <b>∠</b> | <b>,_</b> i | Σ              | Z         | ζ Ω            | <b>L</b> , [   | ¥              | S           | <b>—</b>       | · <u>=</u>  | >         | . 1      | <b>:</b> ; | ×        | >              | 7          | t      |

| AUXILIARY APPLICATION (AA) | GND  | NN.  | - 2 2      | 2 PA 1  | 2 CA 2     | 2 CB 2 | 7 PR 7                                        | 2 TO C     | , and ,                                 | 2 FD 5      | Z PB I   | 2 PA 7      | 2 PA 5         | 2 DA 3    | 200            | CT 2           | CBI            | 3 PB 2      | 3 PB 0         | 3 PA 6      | 3 PA 3    | 2 DA 4   | + 171 /    | 3 PA 5   |                | 3 PB 7 (B) |        |

| AUX                        |      | ٠,   | 4 0        | Λ.      | <b>3</b> † | ~      | ٧                                             | , ,        | . 0                                     | 0 0         |          | 0           | 11             | 2         | 1 5            | 1 :            | <b>†</b>       | 15          | 91             | - 1         | <u>~</u>  | 9 0      | . (        | 20       | 21             | 22         |        |

| 3                          | +5V  | 00   | ;lã        | 5 8     | s          | ၁၉     | 10                                            | <u> 7 </u> |                                         | ) 8         |          | Audio In    | Audio Out (LO) | RCN-1 (1) | Audio Out (H1) | TTV VB DTM (.) | (+) NIN QV III | TTY PTR (+) | TTY KB RTN (-) | TTY PTR (-) | KB ROW 3  | KB COL G | , W. C.    | ND KOW Z | KB COL C       | KB ROW 1   |        |

| A) NOIL                    | ∢    | ď    | ۱ (        | ) (     | וב         | ъ      | ĮΤ                                            | Ι          | ŗ.                                      | <b>Y</b>    | ۲.       | 7           | Z              | Z         | <u>C</u>       | - Δ            | ረ ፡            | S           | H              | n<br>o      | FV        |          |            |          |                |            |        |

| APPLICATION (A)            | GND  | APA3 | A DA 2     | 4 D A 1 | יייי       | APA4   | APA5                                          | APA6       | APA7                                    | APRO        | A Da 1   | מאַל -      | APB2           | APB3      | APB4           | ADAO           | 017.117        | APB7        | APB5           | KB ROW      | KB COL    | KB COL   | יסט מא     | 100 CV   | KB COL         | KB COL     |        |

|                            | 1    | 7    | æ          | ۰.      | <b>.</b>   | ^      | 9                                             | 7          | 00                                      | 6           | , ⊆      | 2 ;         | Ţ              | 12        | 13             | 7              | - L            | 2           | 16             | 17          | <u>18</u> | 19       | 20         | 9 .      | 71             | 22         |        |

| (E)                        | AB0  | ABI  | AB2        | A B 3   | 700        | ₩Q.    | AB5                                           | AB6        | AB7                                     | AB8         | A B9     | (01)        | ABIO           | ABII      | AB12           | AB13           | ); c           | Abia        | ABIS           | B           | R/W       | R/W      | AIID TEST  |          | 21             | Ram-R/W    |        |

| -                          | ٧    | മ    | U          | 2       | ם נ        | L) I   | <u>, , , , , , , , , , , , , , , , , , , </u> | Ξ          | Г                                       | ¥           | <b>-</b> | <b>:</b>    | Ξ              | Z         | O,             | 2              | ί ο            | n 1         | _              | ⊃           | >         | ≱        | ×          | ( )      | <b>&gt;-</b> 1 | 7          |        |

| EXPANSION                  | SYNC | RDY  | ą          | IRO     | Y C        | 2      | ZWZ                                           | RES        | DB7                                     | DB6         | DB5      | 3 6         | DB4            | DB3       | DB2            | DBI            | 900            | og :        |                | DBOUT (I)   | POR       | Unused   | Linused    | 20011    | V (+           | GND        |        |

|                            | -    | 7    | 'n         | 7       | · 1/       | ``     | Ð                                             | ^          | ∞                                       | 6           | 9        | ) <u>-</u>  | <b>-</b> :     | 7.7       | 13             | †I             | L/             | 1:          | 9 !            | 17          | ×         | 19       | 20         | ; 7      | 17             | 77         |        |

(1) Jumper option (B) Buffered

99

|                                             | TABI      | LE 4-2. CONNECTOR PC | SINTS | TABLE 4-2. CONNECTOR POINTS AND THEIR FUNCTIONS IN SYM-1 (Continued) | -1 (Co   | ntinued)     |

|---------------------------------------------|-----------|----------------------|-------|----------------------------------------------------------------------|----------|--------------|

|                                             | POWER (P) |                      | •     | TERMINAL (T)                                                         | KEYB     | KEYBOARD (K) |

| 7.5                                         | <b>∀</b>  | TVP (ontional)       | J     | GND                                                                  |          | +5V          |

| ֡֝֝֝֝֓֓֓֓֓֓֓֓֓֓֓֓֓֓֓֓֓֓֓֓֓֓֓֓֓֓֓֡֓֓֓֓֓֓֡֓֓֡ | ζ α       | CND                  | _     | RS-232 IN                                                            | 7        | +5V          |

| 25.5                                        | a C       | +5V                  |       | RS-232 OUT                                                           | ٣        | +5V          |

| , C                                         | ے د       | 4 CND                |       | N.C.                                                                 | <b>.</b> | +54          |

| 754                                         | ш         | -VN (optional) 5     |       | . A5+                                                                | ٠ ک      | 4V+          |

|                                             | ļ         | 9 CNU                |       | +5V                                                                  | 9        | +VP          |

| į                                           | -1        | 7                    | _     | GND                                                                  | _        | NA-          |

|                                             |           | ∞                    |       | +5V                                                                  | ∞        | N^-          |

|                                             |           | 0                    | _     | TTY Keyboard IN +                                                    | 6        | GND          |

|                                             |           | I                    | 0     | TTY Keyboard IN -                                                    |          | GND          |

|                                             |           |                      |       | TTY Printer OUT -                                                    |          | GND          |

|                                             |           |                      |       | TTY Printer OUT +                                                    | 12       | GND          |

|                                             |           |                      | 2 :   |                                                                      |          | RS-232 IN    |

|                                             |           |                      |       | Audio Remote NPN HI                                                  |          | RS-232 OUI   |

|                                             |           |                      | [2    | Audio Remote NPN LO                                                  |          |              |

|                                             |           |                      | 91    | Audio Remote PNP LO                                                  |          |              |

|                                             |           |                      |       | Audio Remote PNP HI                                                  |          |              |

|                                             |           | •                    |       | Audio IN                                                             |          |              |

|                                             |           | ,                    |       | Audio GND                                                            |          |              |

|                                             |           | . •                  |       | N.C.                                                                 |          |              |

|                                             |           | . •                  | 21    | Audio Out (HI)                                                       |          |              |

|                                             |           |                      |       | N.C.                                                                 |          |              |

|                                             |           |                      |       | Audio Out (LO)                                                       |          |              |

|                                             |           |                      |       | N.C.                                                                 |          |              |

|                                             |           |                      |       | Audio GND                                                            |          |              |

タンキョファ

Figure 4-2. TTY/CRT INTERFACE SCHEMATIC

Figure 4-3. AUDIO CASSETTE INTERFACE SCHEMATIC

Figure 4-4. AUDIO CASSETTE REMOTE CONTROL

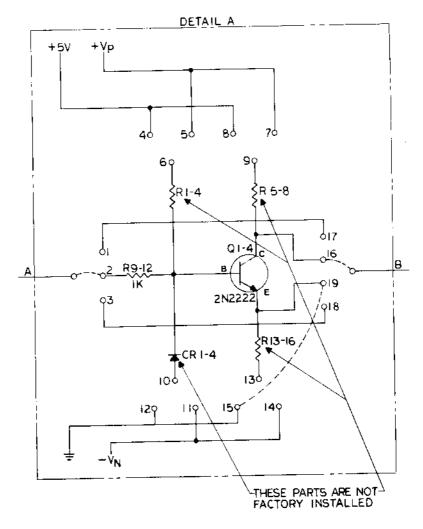

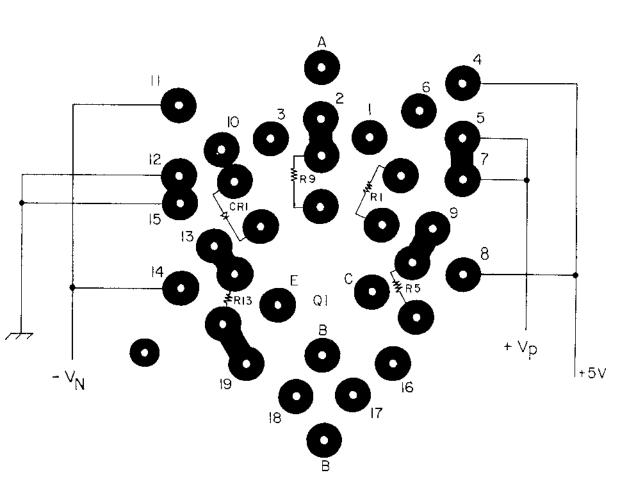

### I/O BUFFERS

Figure 4-5. I/O BUFFERS SCHEMATIC

Figure 4-5a. I/O BUFFERS, PC LAYOUT BLOW-UP

Figure 4-6. KEYBOARD/DISPLAY SCHEMATIC

Figure 4-7. CONTROL SECTION SCHEMATIC

### OSCILLOSCOPE OUTPUT DRIVER

Figure 4-9. OSCILLOSCOPE OUTPUT DRIVER SCHEMATIC

### 4.2 MEMORY ALLOCATION

This section describes the standard memory allocation in your SYM-1 microcomputer system. It makes extensive use of the detailed Memory Map contained in Figure 4-10. Also described in this section is the technique by which ROM and RAM addressing and usage may be altered by using an array of on-board jumpers which allow you to modify and expand your SYM-1 memory. Expanding RAM memory using off-board components is taken up briefly in Section 4.2.3, although a detailed discussion of this is reserved for Chapter 8, "System Expansion".

### 4.2.1 Standard Memory Allocation

Figure 4-10 is a map of the standard memory allocation in your SYM-1 microcomputer. Provided with your system are 1K of on-board RAM, extending from location 0000 to 03FF in the Memory Map. Note that the top-most eight bytes (locations 00F8 to 00FF) in Page Zero of this 1K block are reserved for use by the system and should not be used by your programs. The remainder of Page Zero is largely similar to the rest of the RAM provided, but it also has some special significance for addressing which will become clearer in Section 4.3. Locations 0100-01FF in the 1K memory block furnished with your system are reserved for stack usage. Your programs may use this area, but you should use it for normal stack operations incidental to operating your programs. Locations 0200-03FF are general-use RAM for your program and data storage.

In addition to the 1K of on-board RAM furnished with your system, sockets are provided for 3K of plug-in RAM, allowing you to have 4K of on-board RAM memory. These sockets occupy memory locations 0400-0FFF.

The SUPERMON monitor resides in ROM at memory locations 8000-8FFF. (As you know, the SY6502 CPU addresses all memory and I/O identically, so that it is immaterial whether a specific address location is occupied by RAM, ROM or I/O devices.) The next 4K block, from 9000-9FFF, is reserved for future expasion of SUPERMON, although you may use those locations if you wish to do so, provided you remember that if you should obtain an expanded SUPERMON system in the future these addresses may be used.

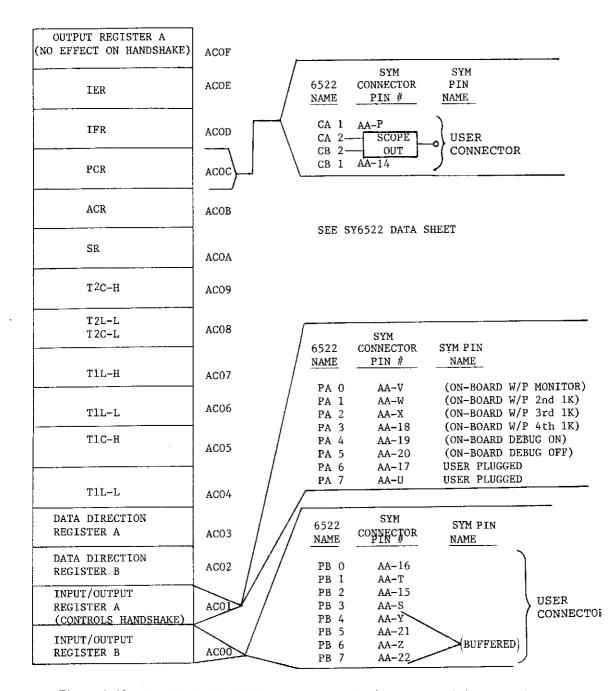

Extending from A000-AFFF are the I/O devices on your SYM-1 module. As we have previously said, each port on the SY6522/SY6532 devices in SYM-1 is an addressable location. Sheets 2-6 of Figure 4-10 provide you with a detailed Memory Map breakdown of how these devices are addressed. Note that within the SY6532 is a 128 byte segment (locations A600-A7FF). This is the RAM which is resident on the SY6532 used by SYM-1 as System RAM. Sheet 4 of Figure 4-10 describes each memory location within System RAM in detail; you will need this data if you wish to make use of the capability of the system for modifications to SUPERMON. These modifications may include creating your own commands (as described in Chapter 5) which may be entered as if they were Monitor commands. Other such modifications making use of System RAM locations are described in Chapter 9 of this manual.

Memory locations B000-F880 may be used by your programs, provided of course you have expanded memory to fill those address locations (see Chapter 8). Note, however, that if you plan to obtain the Synertek Systems 8K BASIC module at some later date, that module will occupy locations C000-DFFF. You should plan your applications programs accordingly. Locations FB80-FFFF are reserved for special use by the system, and should not be used in any of your applications code.

Figure 4-10. STANDARD MEMORY MAP, SYM-1

Figure 4-10 (Cont'd). MEMORY MAP FOR SY6522 VIA #1 (DEVICE U25)

Figure 4-10 (Cont'd). MEMORY MAP FOR SY6532 (DEVICE U27)

| SYMBOL          | ADDRESS              | DEFAULT<br>VALUE | COMMENTS                                                        |

|-----------------|----------------------|------------------|-----------------------------------------------------------------|

| IRQVEC          | A67F                 | 80               | IRQ Vector                                                      |

| RSTVEC          | A67E<br>A67D<br>A67C | 0F<br>8B<br>4A   | RESET Vector                                                    |

| NMIVEC          | A67B<br>A67A         | 80<br>9B         | NMI Vector                                                      |

| UIRQVC          | A679<br>A678         | 80<br>29         | User IRQ Vector                                                 |

| UBRKVC          | A677<br>A676         | 80<br>4A         | User Break Vector                                               |

| TRCVEC          | A675<br>A674         | 80<br>C0         | Trace Vector                                                    |

| EXEVEC          | A673                 | 88<br>7E         | 'Execute' Vector                                                |

| SCNVEC          | A672<br>A671<br>A670 | 89<br>06         | Display Scan Vector                                             |

| URCVEC          | A66F<br>A66E         | 4C<br>81         | University of Command Veston                                    |

|                 | A66D<br>A66C         | D1<br>4C         | Unrecognized Command Vector                                     |

| URSVEC          | A66B<br>A66A<br>A669 | D1<br>81<br>4C   | Unrecognized Syntax Vector                                      |

| INSVEC          | A668<br>A667         | 89<br>6A         | In Status Vector                                                |

| OUTVEC          | A666<br>A665<br>A664 | 4C<br>89<br>00   | Output Vector                                                   |

| INVEC           | A663<br>A662<br>A661 | 4C<br>89<br>BE   | Input Vector                                                    |

| YR              | A660<br>A65F         | 4C               |                                                                 |

| XR<br>AR        | A65E<br>A65D         | 00               |                                                                 |

| FR<br>SR        | A65C<br>A65B         | 00<br>FF         | User Registers                                                  |

| PCHR<br>PCLR    | A65A<br>A659         | 8B<br>4A         | (No. 1)                                                         |

| MAXRC<br>LSTCOM | A658<br>A657         | 10<br>00         | Max. No. Bytes/Record, Paper Tape (Note 6) Last Monitor Command |

| TV<br>KSHFL     | A656<br>A655         | 00               | Trace Velocity (Note 5) Hex Keyboard Shift Flag                 |

| TOUTFL<br>TECHO | A654<br>A653         | 80<br>80         | In/Out Enable Flags (Note 4) Terminal Echo (Note 3)             |

| ERCNT<br>SDBYT  | A652<br>A651         | 00<br>4C         | Error Count (Note 2)  Baud Rate (Note 1)                        |

| PADBIT          | A650                 | 01               | Number of Padbits on Carriage Return                            |

Figure 4-10. SYSTEM RAM MEMORY MAP, SY6532

| SYMBOL                                 | ADDRESS                              | DEFAUL<br>VALUE      | · ·                                                   |

|----------------------------------------|--------------------------------------|----------------------|-------------------------------------------------------|

| P1H<br>P1L<br>P2H<br>P2L<br>P3H<br>P3L | A64F<br>A64E<br>A64D<br>A64C<br>A64B | 00<br>00<br>00<br>00 | 16-Bit Parameters                                     |

| PARNR                                  | A64A<br>A649                         | 00                   | No. of Parameters Entered                             |

|                                        | A648<br>A647<br>A646                 | 00                   | Not Used                                              |

| RDIG<br>DISBUF                         | A645<br>A644                         | 06<br>86             | Right-most Digit of Display Buffer                    |

|                                        | A643<br>A642<br>A641                 | 6E<br>6D<br>00       | Display Buffer                                        |

| SCRF                                   | A640<br>A63F                         | 00                   |                                                       |

| SCRE<br>SCRD                           | A63E<br>A63D                         | 00                   | Monitor Scratch Locations                             |

| TAPET2<br>SCRB                         | A63C<br>A63B                         | 5A<br>00             | High Speed Tape Waveform                              |

| SCR6                                   | A636                                 | 00                   | Monitor Scratch Locations                             |

| TAPET1<br>SCR4                         | A635<br>A634                         | 33<br>00             | High Speed Tape Waveform<br>Monitor Scratch Locations |

| SCR3<br>HSBDRY                         | A633<br>A632                         | 00<br>46             | High Speed Tape Boundary                              |

| KMBDRY<br>TAPDEL                       | A631<br>A630                         | 2C<br>04             | KIM Tape Boundary<br>High Speed Tape Leader           |

| JTABLE                                 | A62F<br>A62E                         | 00<br>D0             | User Socket P3 (Jump Entry No. 7)                     |

|                                        | A62D<br>A62C                         | C8<br>00             | User Socket P2 (Jump Entry No. 6)                     |

|                                        | A62B<br>A62A                         | 03<br>00             | 0300 (Jump Entry 5)                                   |

|                                        | A629<br>A628                         | 02<br>00             | 0200 (Jump Entry 4)                                   |

| •                                      | A627<br>A626                         | 00                   | 0000 (Jump Entry 3)                                   |

|                                        | A625<br>A624                         | 8B<br>64             | NEWDEV (Jump Entry 2) (Note 7)                        |

|                                        | A623<br>A622                         | 8B<br>A7             | TTY (Jump Entry 1)                                    |

|                                        | A621                                 | C0                   | BASIC (Jump Entry 0)                                  |

| SCPBUF                                 | A620<br>A61F                         | 00                   |                                                       |

|                                        | A600                                 |                      | Scope Buffer, No Defaults (32 locations)              |

Figure 4-10. SYSTEM RAM MEMORY MAP, SY6532 (Continued)

### NOTES - SYSTEM RAM

| 1. | BAUD RATE | <b>-</b> | BAUD<br>110<br>300<br>600<br>1200<br>2400<br>4800 | SDBYT<br>D5<br>4C<br>24<br>10<br>06                          |                                                                                          |

|----|-----------|----------|---------------------------------------------------|--------------------------------------------------------------|------------------------------------------------------------------------------------------|

| 2. | ERCNT     | -        | Count of by                                       | P, FILL, B MOV<br>tes which failed to<br>checksums up to \$. |                                                                                          |

| 3. | TECHO     | -        |                                                   | IO/NO ECHO PUT/NO OUTPUT                                     | This bit is toggled everytime a control O (ASCII 0F) is encountered in the input stream. |

4. TOUTFL - bit 7 = enable CRT IN

bit 6 = enable TTY IN

bit 5 = enable TTY OUT

bit 4 = enable CRT OUT

5. TV - TRACE VELOCITY

00 = SINGLE STEP

non-zero - PRINT PROGRAM COUNTER AND ACCUMU-LATOR THEN PAUSE AND RESUME

PAUSE DEPENDS ON TV (TRY TV = 09)

- 6. USER PC DEFAULT = 8B4A = RESET

- 7. NEW DEV TO CHANGE BAUD RATE ON RS-232 INTERFACE.

Figure 4-10. SYSTEM RAM MEMORY MAP, SY6532 (Continued)

Figure 4-10. MEMORY MAP FOR SY6522 VIA #2 (DEVICE U28-USER SUPPLIED) (Continued)

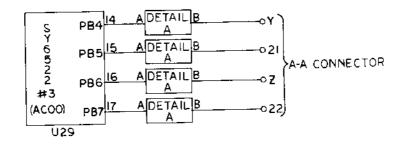

Figure 4-10. MEMORY MAP FOR SY6522 VIA #3 (DEVICE U29) (Continued)

### 4.2.2 Address Decoding Jumper Options

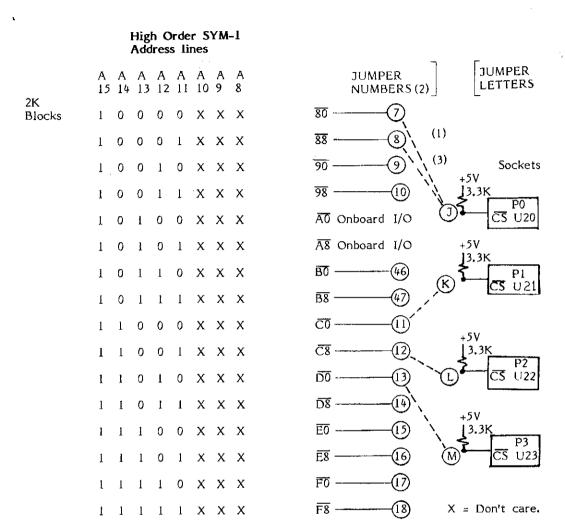

Four sockets (labeled P0-P3 on the board) for ROM, PROM or EPROM are provided with your SYM-1. Each socket may contain any of four different types of Read-Only Memory devices, up to a total of 28K. The four acceptable devices are the SY2716, the SY2316B, the SY2332 and the SY2364. Each device is slightly different, but they are all read-only memories. They may appear in any combination on a SYM-1 microcomputer system, provided their total capacity does not exceed 24K. But since the devices have different memory capacities, it is necessary to alter normal addressing to accomodate the specific devices selected.

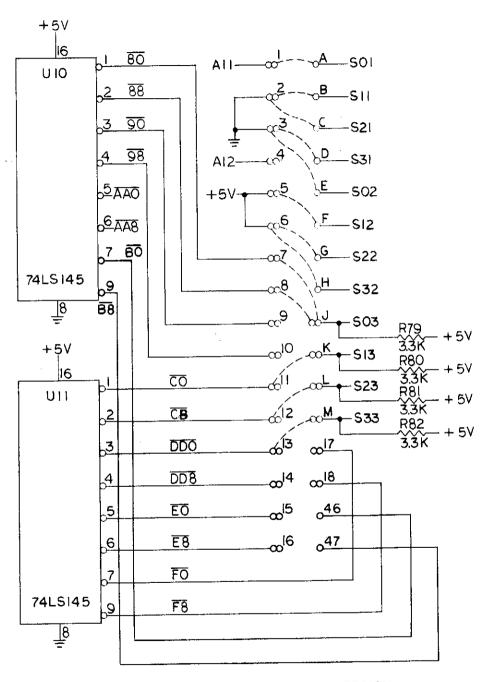

To serve this purpose, we have provided a set of jumpers, located just to the left of the center of the board and directly under the two 74LS145's. The schematic in Figure 4-11 illustrates each useful jumper combination and Table 4-3 outlines them in greater detail. (Note that Table 4-3 contains other jumpers available on the SYM-1, not all of which pertain to memory use.) The broken lines in Figure 4-11 indicate the jumpers installed at the factory. Note, for example, that the first PROM socket, labeled PO (device U20) is associated with the address group beginning with 8000. It it were necessary to change this configuration, you would remove the connection from Pin 1 of the lower address decoder (74LS145) to jumper connection 7-J so that it becomes associated with a jumper combination which addresses the device you wish to address. Table 4-3a will assist you in configuring your selection of ROM correctly.

Near the bottom of the board below the speaker unit are four jumpers labeled JJ, KK, LL and MM. These enable Write Protection on the RAM in the four IK blocks available on the board. Jumper 45-MM is factory-installed, enabling Write Protection on System RAM (the 128-byte block in the SY6532). As you add RAM later, or to Write Protect any of the on-board RAM aside from System RAM, you must connect the appropriate jumpers to enable the Write Protect function on the desired memory locations. RAM may be enabled for Write Protect in IK blocks.

These jumpers offer you flexibility to adapt the SYM-1 board to your particular application. The jumpers will give you the ability to do the following:

- Use 2K, 4K, or 8K byte ROM or PROM in each 24 pin socket.

- Complete flexibility in selecting user PROM addressing.

- Ability to auto power-on to any of the ROM/PROM sockets.

- Write protect expansion RAM.

### 4.2.3 Off-Board Expandability

SYM-1 is expandable, on-board, up to 28K bytes of EPROM/ROM memory and 4K bytes of RAM, with 4K bytes of address space allocated to the on-board I/O devices. Further expansion of any combination of ROM, PROM, RAM or I/O can be implemented by using SYM's "E" (Expansion) connector to attach an auxiliary board containing the additional devices. Total expandability is limited only by the amount of addressing capability of the SY6502 CPU, i.e., 64K bytes.

Detailed instructions for implementing off-board expansion are contained in Chapter 8, "System Expansion."

### 4.2.4 I/O Buffers

Your SYM-1 board comes to you equipped with four specially configured I/O buffer circuits. (See Figure 4-5.) The circuit configuration and PC Board layout allow the user to configure these buffers in many ways.

---- CONFIGURATION OF DELIVERED VERSION

Figure 4-11. MEMORY ADDRESS DECODING JUMPER OPTIONS

### Table 4-3. SYM-1 JUMPERS

| JUMPER<br>LETTER     | POSITION<br>NUMBER                  | DESCRIPTION                                                                                                                                                             |

|----------------------|-------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| A,B,C,D<br>E,F,G,H   | 1,2,3<br>4,5,6                      | PROM/ROM Device Select<br>(See Table 4-3a)                                                                                                                              |

| J,K,L,M              | 7,8,9,10,11,12<br>13,14,15,16,17,18 | ADDRESS SELECT<br>(See Table 4-3b)                                                                                                                                      |

| N                    | 19 (1)<br>20                        | Auto Power-On to U20 (2)<br>Disable Auto Power-On to U20                                                                                                                |

| P                    | 19 (1)<br>20                        | Auto Power-On to U21 (2)<br>Disable Auto Power-On to U21                                                                                                                |

| R                    | 19 (1)<br>20                        | Auto Power-On to U22 (2)<br>Disable Auto Power-On to U22                                                                                                                |

| S                    | 19 (1)<br>20                        | Auto Power-On to U23 (2)<br>Disable Auto Power-On to U23                                                                                                                |

| T<br>U               | 21<br>22                            | Enables Monitor RAM at A0xx (3)<br>Enables Monitor RAM at F8xx (3)                                                                                                      |

| V                    | 23                                  | RCN-I to connector A-N                                                                                                                                                  |

| w<br>X               | 24<br>25                            | Enables Software Debug ON<br>Enables Software Debug OFF                                                                                                                 |

| Y                    | 26                                  | DBOUT to connector E-17                                                                                                                                                 |

| BB<br>CC             | 31<br>32                            | Connects TTY IN to PB6 @A402<br>Connects CRT IN to PB7 @A402                                                                                                            |

| DD                   | 33<br>34                            | To run TTY @ +5V and GND<br>To run TTY @ +5V and -Vn (4)                                                                                                                |

| EE                   | 35<br>36                            | To run TTY @ +5V and -Vn (4)<br>To run TTY @ +5V and GND                                                                                                                |

| FF                   | 37<br>38                            | To run TTY @ +5V and GND<br>To run TTY @ +5V and -Vn (4)                                                                                                                |

| GG                   | 39<br>40                            | To run RS232 @+5V and GND<br>To run RS232 @+5V and -Vn (5)                                                                                                              |

| нн                   | 41                                  | Decode line $\overline{18}$ to connector A-K                                                                                                                            |

| JJ<br>KK<br>LL<br>MM | 42<br>43<br>44<br>45                | Enable software write protect 3K block<br>Enable software write protect 2K block<br>Enable software write protect 1K block<br>Enable software write protect monitor RAM |

### Table 4-3. SYM-1 JUMPERS (Continued)

### **NOTES**

- Only one socket (U20, U21, U22, U23) should be jumpered to position 19 at one time. The remaining three sockets should be jumpered to position 20.

- See software consideration of auto power-on in Chapter 9.

- 3 One or both can be connected at the same time.

- These positions require a recommended -9V to -15V supply applied to the power connector pin E. R107 should be adjusted (removed and replaced) for your proper current loop requirements.

Example: (for 60ma current loops and Vn = -10V)

a. Connect DD to 33 EE to 35 FF to 38

b. R107 =  $\frac{\text{Vn } -5\text{V}}{\text{I}} = \frac{(10 -5)}{60 \text{ ma}} = 100$

R107 = 300x (as installed) for 20 ma current loop and Vn=-10V

For RS232 devices using other than LM1489 or equivalent input receivers (i.e., probably terminals older than ten years) then GG should be strapped to 40 and a -9V to -15V supply applied to the power connector pin E.

Table 4-3a. SYM-1 PROM/ROM DEVICE SELECT

| SOCKET<br>LOCATION | SOCKET<br>NAME | MEMORY<br>DEVICE | JUMPER<br>LETTER | POSITION<br>NUMBER |

|--------------------|----------------|------------------|------------------|--------------------|

| U20                | Р0             | 2716             | A<br>E           | 2 or 3<br>5 or 6   |

| U20                | PO             | 2316             | A<br>E           | 2 or 3<br>2 or 3   |

| U20                | PO             | 2332             | A<br>E           | 1<br>2 or 3        |

| U20                | PO             | 2364             | A<br>E           | 1<br>4             |

| U21                | Pi             | 2716             | B<br>F           | 2 or 3<br>5 or 6   |

| U21                | Pl             | 2316             | B<br>F           | 2 or 3<br>2 or 3   |

| U21                | Pl             | 2332             | B<br>F           | l<br>2 or 3        |

| U21                | P1             | 2364             | B<br>F           | 1<br>4             |

| U22                | P2             | 2716             | C<br>G           | 2 or 3<br>5 or 6   |

| U22                | P2             | 2316             | C<br>G           | 2 or 3<br>5 or 6   |

| U22                | P2             | 2332             | C<br>G           | 1<br>2 or 3        |

| U22                | P2             | 2364             | C<br>G           | 1<br>4             |

| U23                | Р3             | 2716             | D<br>H           | 2 or 3<br>5 or 6   |

| U23                | Р3             | 2316             | D<br>H           | 2 or 3<br>2 or 3   |

| U23                | Р3             | 2332             | D<br>H           | 1<br>2 or 3        |

| U23                | ₽3             | 2364             | D<br>H           | 1<br>4             |

NOTE: 2716 devices assumes Synertek, Intel or equivalent pin outs.

Table 4-3b. SYM-1 ADDRESS SELECT

### NOTES:

- (1) Broken lines indicate delivered version of jumpers.

- (2) Each jumper number represents a 2K address space decode.

- (3) Jumper numbers can be wire or'ed to increase the address space of the  $\overline{CS}$  on any socket (i.e., decoder is open collector.)

The single-stage circuit consists of a transistor and "circuit positions" for the user to add resistors, capacitors and dioders in any of many positions. This flexibility allows inverting and noninverting stages, input-resistive or capacitive coupling and much more. The user should refer to the schematic and P.C. layout in Figure 4-5a in order to completely understand this circuit.

### 4.3 SOFTWARE DESCRIPTION

Software on your SYM-1 microcomputer must be discussed from two perspectives. First, the SYM SUPERMON Monitor software which handles keyboard display, interrupts and other requirements for system operation must be understood. We will discuss this subject in succeeding sections. The second aspect of software is the microprocessor assembly language with which you will write your applications programs. A brief introduction to the 6502 instruction set is included later in this chapter.

In this chapter, we discuss the SYM-1 command language syntax only briefly; Chapter 5 contains a detailed discussion of each of the instructions in the set. Chapter 6 will help you through the process of using these and the 6502 language in applications programming by describing three selected sample programs.

### 4.3.1 Monitor Description - General

Figure 9-1 illustrates the general system flow of the SYM-1 SUPERMON Monitor software. As you can tell, the main program is simple and straightforward. Its purpose is to direct processing to the appropriate I/O or command routine, and for this reason it is thought of as a "driver"—it "drives" or directs the software.

The means by which the Monitor handles the direction of software flow is one of the unique features of the SYM-1 system and is worth a brief explanation at this point. We will discuss the subject in greater detail in Chapters 5 and 8.

When the SUPERMON Monitor receives a one- or two-character command from the on-board keyboard, TTY or CRT terminal, it then accepts 0-3 parameters associated with the command. The string of command and parameters (if any) is terminated by a carriage return. It is noteworthy that each instruction which may be entered by use of a single key on the on-board keyboard may also be entered with a similar command from a terminal.

Upon receiving a command and up to three parameters, SUPERMON checks to determine whether the command and its associated number of parameters is a defined combination. If so, the command is executed. Otherwise, an error message is printed or displayed showing the ASCII representation of the command which was not recognized.

For example, a "GO" with one parameter causes the program to pass control to the program stored at the memory location indicated by the parameter. Thus, a "GO" followed by "0200" instructs the system to begin executing the instructions stored starting at memory location 0200. A "GO" with no parameters (i.e., "GO" followed by a Carriage Return) will cause program execution to resume at the address stored in the "pseudo Program Counter" (memory locations A659 and A65A).

However, a "GO" command with two or three parameters is not a defined command in SUPERMON, and will result in a display or message of "Er 47". The "47" is the ASCII representation for a "G" and is designed to help you define the instruction or command which was not recognized.

The monitor is designed so that you can extend the range of defined command-parameter combinations by "intercepting" the error routine before it executes and designing your own series of pointers to memory locations to be associated with specific commands. Thus, you might wish to define a "GET" routine which could be entered at the keyboard with a "GO" and two parameters. You will learn how to do this in Chapter 9.

### 4.3.2 Software Interfacing

The SYM-1 Monitor is structured to be device-independent. Special requirements for device handling are "outside" the Monitor's central control routines, which isolate them from the Monitor's standard functions. Also, as we have indicated, SYM-1 commands may be entered from any device. It is not necessary to use the on-board keyboard to do so. This means you need not concern yourself with the details of I/O; they are handled internally.

### 4.3.3 6502 Microprocessor Assembly Language Syntax

The SY6502 microprocessor used on your SYM-1 is an eight-bit CPU, which means that eight bits of data are transferred or operated upon at a time. It has a usable set of 56 instructions used with 13 addressing modes. Instructions are divided into three groups.

Group One instructions, of which there are eight, are those which have the greatest addressing flexibility and are therefore the most general-purpose. These include Add With Carry (ADC), the logical AND (AND), Compare (CMP), the logical Exclusive OR (EOR), Load A (LDA), logical OR with Accumulator (ORA), Subtract With Carry (SBC) and Store Accumulator (STA).

Group Two instructions include those which are used to read and write data or to modify the contents of registers and memory locations.

The remaining 39 instructions in the SY6502 instruction set are Group Three instructions which operate with the X and Y registers and control branching within the program. You'll learn more about these instructions in the next section. More detailed information can be found in the Synertek Programming Manual for the SY6500 family.

An assembly language instruction consists of the following possible parts:

Optional. Used to allow branching to the line containing the label Label and for certain addressing situations.

Required. The mnemonic is a three-character abbreviation which Mnemonic represents the instruction to be carried out. Thus the mnemonic to store the contents of the accumulator in a specific memory

location is "STA" (STore Accumulator).

Some may be required, or none may be allowed. This depends Operand(s) entirely upon the instruction itself and may be determined from the later discussion.

Separated from last operand (or from the command Comment mnemonic where no operand is used) by at least one blank. These words are ignored by the assembler program but are included only to allow the programmer and others to understand the program.

The SY6502 allows 13 modes of addressing, which makes it one of the most flexible CPUs on the market. Table 4-4 describes these addressing modes briefly. Details may be found in the Synertek Programming Manual for the SY6500 family.

You will note that some of the addressing modes make use of Page Zero, a concept introduced briefly earlier in this chapter. Page Zero addressing modes are designed to reduce memory requirements and provide faster execution. When the SY6502 processor encounters an instruction using Page Zero addressing, it assumes the high-order byte of the address to be 00, which means you need not define that byte in your program. This technique is particularly useful in dealing with working registers and intermediate values. As the Memory Map (Figure 4-10, Sheet 1) shows, memory locations 0000-00FF make up Page Zero.

### 4.3.4 SY6502 Instruction Set

Table 4-5 provides you with a summary of the SY6502 instruction set. Each instruction is shown with its mnemonic, a brief description of the function(s) it carries out, and the corresponding "op code" for each of its valid addressing modes. The "op code" is the hexadecimal representation of the instruction and is what will appear when the instruction byte is displayed by SUPERMON.

When creating applications programs for your SYM-1, you will typically write them in the SY6502 assembly language mnemonic structure shown in Table 4-5, then perform a "hand assembly" to generate the "op codes" and operands. The process of hand assembling code is explained in greater detail in Section 6.2.2. You will be referring to this table—or to your SYM Reference Card—quite frequently during programming.

To understand some of the instructions, you should be aware of six "status register" flags which are set and reset by the results of program execution. Generally, these flags and their functions are:

N - Set to "I" by CPU when the result of the previous instruction is negative

Z - Set to "1" by CPU when the result of the previous instruction is zero

C - Set to "1" by CPU when the previous instruction results in an arithmetic "carry"

Set to "0" by CPU when the previous instruction results in "borrow" (subtract)

Also modified by shift, rotate and compare instructions.

I - When "1," IRQ to the CPU is held pending

D - When "1," CPU arithmetic is operates in decimal mode

V - Set to "I" by CPU when the result of the previous instruction causes an arithmetic overflow

The Synertek Programming Manual (MNA-2) discusses this subject in greater detail.

# Table 4-4. SUMMARY OF SY6502 CPU ADDRESSING MODES

### SY6502 INSTRUCTION SET SUMMARY

### Addressing Modes

|             | ×                                                      |                                                 | ate                                                         | age<br>1 page zero                                                                          | iexed                                                                                                                                    | lexed<br>ero                                                                                                                             | ıte                                                                                   |

|-------------|--------------------------------------------------------|-------------------------------------------------|-------------------------------------------------------------|---------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------|

| 1e          | Code for transfer A to X                               | Code for rotate left A                          | Code for load A immediate<br>Constant to use                | Code for load A zero page<br>Low part of address on page                                    | Code for zero page indexed<br>by X<br>Base address on page zero                                                                          | Code for zero page indexed<br>by Y<br>Base address on page zero                                                                          | Code for load A absolute<br>Low part of address<br>High part of address               |

| Example     | A.A. Co                                                | 2A Co                                           | A9 Co                                                       | A5 Co<br>75 Lo                                                                              | B5 Co                                                                                                                                    | B6 Cc                                                                                                                                    | AD Co<br>47 Lo<br>02 Hi                                                               |

|             | TAX                                                    | ROL A                                           | LDA #3                                                      | LDA Z                                                                                       | LDA Z,X                                                                                                                                  | LDX Z,Y                                                                                                                                  | LDA L                                                                                 |

| #<br>Bytes  | *                                                      | -1                                              | 7                                                           | 8                                                                                           | 0                                                                                                                                        | 7                                                                                                                                        | ю                                                                                     |

| Description | The operation performed is implied by the instruction. | The operation is performed upon the A register. | The data accessed is in the second byte of the instruction. | The address within page zero of the data accessed is in the second byte of the instruction. | The second byte of the instruction plus the contents of the X register (without carry) is the address on page zero of the data accessed. | The second byte of the instruction plus the contents of the Y register (without carry) is the address on page zero of the data accessed. | The address of the data accessed is in the second and third bytes of the instruction. |

| Mode        | IMPLIED                                                | ACCUMULATOR                                     | IMMEDIATE                                                   | ZERO PAGE                                                                                   | ZERO PAGE<br>INDEXED BY X                                                                                                                | ZERO PAGE<br>INDEXED BY Y                                                                                                                | ABSOLUTE                                                                              |

\*Except BRK which is two bytes when not using SUPERMON or when in DEBUG mode.

# Table 4-4. SUMMARY OF SY6502 CPU ADDRESSING MODES (Continued)

| #<br>Bytes Example | und third 3 LDA L,X BD Code for load A indexed by X lius the 47 Low part of base address is the 02 High part of base address ed.       | nd third 3 LDA L,Y B9 Code for load A indexed by Y lus the 47 Low part of base address is the 02 High part of base address ed.        | ruction 2 LDA (Z,X) Al Code for load A, indirect preregister indexed by X ress on 75 Base address on page zero                                                   | ro two- 2 LDA (Z),Y Bl Code for load A, indirect he post-indexed by Y ion, 75 Base address of page zero ata                                                              | ruction 2 BEQ LOC FO Code for branch if equal<br>es) to 07 Seven bytes ahead        | nd 3 JMP (LOC) 6C Code for jump indirect ion 47 Low part of indirect address ss            |

|--------------------|----------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------|

|                    | rd.                                                                                                                                    | ฑ                                                                                                                                     |                                                                                                                                                                  | ı                                                                                                                                                                        | E                                                                                   |                                                                                            |

| Description        | The address in the second and thirr bytes of the instruction, pius the contents of the X register is the address of the data accessed, | The address in the second and thir bytes of the instruction, plus the contents of the Y register is the address of the data accessed. | The second byte of the instruction plus the contents of the X register (without carry) is the address on page zero of the two-byte address of the data accessed. | The contents of the page zero two byte address specified by the second byte in the instruction, plus the contents of the Y register is the address of the data accessed. | The second byte of the instructio contains the offset (in bytes) to branch address. | The address in the second and third bytes of the instruction is the address of the address |

| Mode               | INDEXED BY X                                                                                                                           | INDEXED BY Y                                                                                                                          | INDIRECT<br>PRE-INDEXED<br>BY X                                                                                                                                  | INDIRECT<br>POST-INDEXED<br>BY Y                                                                                                                                         | RELATIVE<br>BRANCH                                                                  | INDIRECT JUMP                                                                              |

Table 4-5. SY6502 CPU Instruction Set Summary

|                              |             |                                                       |                                         |                                                                                     |                                            |                                        |                                            | <del></del>                                                                              |                                             |                                                |                                            |                                        |

|------------------------------|-------------|-------------------------------------------------------|-----------------------------------------|-------------------------------------------------------------------------------------|--------------------------------------------|----------------------------------------|--------------------------------------------|------------------------------------------------------------------------------------------|---------------------------------------------|------------------------------------------------|--------------------------------------------|----------------------------------------|

|                              | E)          | ı                                                     | 1                                       | ı                                                                                   | 1                                          | ı                                      | '                                          | -                                                                                        | 1                                           |                                                |                                            |                                        |

|                              | >           | *                                                     | ı                                       | ı                                                                                   |                                            | 1                                      |                                            | ∑ ∑                                                                                      | - '                                         | 1                                              | 1 -                                        |                                        |

| u o                          | Ω           | 1                                                     | ı                                       | 1                                                                                   |                                            | 1                                      | ł                                          | 1                                                                                        | 1                                           | <u> </u>                                       | <u>'</u>                                   |                                        |

| Condition<br>Codes           | н           | 1                                                     | ι                                       | 1                                                                                   | 1                                          | 1                                      | 1                                          | ·                                                                                        | 1                                           | <br>                                           |                                            | -                                      |

| Co                           | υ           | *                                                     | ı                                       | *                                                                                   | '                                          | l                                      | 1                                          | 1                                                                                        | 1                                           | 1                                              |                                            |                                        |

| රි                           | Z           | *                                                     | *                                       | *                                                                                   | 1                                          | ı                                      | 1                                          | *                                                                                        | 1                                           | 1                                              |                                            |                                        |

|                              | Z           | *                                                     | *                                       | *                                                                                   | 1                                          | ı                                      | 1                                          | M7                                                                                       | 1                                           | 1                                              | 1                                          |                                        |

|                              | IND         |                                                       |                                         |                                                                                     |                                            |                                        |                                            |                                                                                          |                                             |                                                |                                            |                                        |

|                              | BET         |                                                       |                                         |                                                                                     | 06                                         | <u>а</u>                               | <u>ы</u>                                   |                                                                                          | 30                                          | 8                                              | 2                                          |                                        |