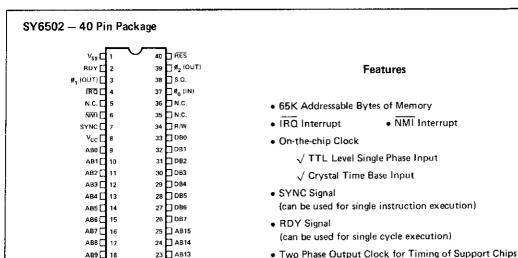

# APPENDIX I SY6502 DATA SHEET

## 8-Bit Microprocessor **Family**

### SY6500

### MICROPROCESSOR **PRODUCTS**

**APRIL 1979**

- Single 5 V ±5% power supply

- N channel, silicon gate, depletion load technology

- Eight bit parallel processing

- 56 Instructions

- Decimal and binary arithmetic

- Thirteen addressing modes

- True indexing capability

- Programmable stack pointer

- Variable length stack

- Interrupt capability

- Non-maskable interrupt

- Use with any type or speed memory

- Bi-directional Data Bus

- Instruction decoding and control

- Addressable memory range of up to 65 K bytes.

- "Ready" input

- Direct memory access capability

- Bus compatible with MC6800

- Choice of external or on-board clocks

- 1 MHz, 2 MHz, and 3 MHz operation

- On-chip clock options

- \* External single clock input

- \* Crystal time base input

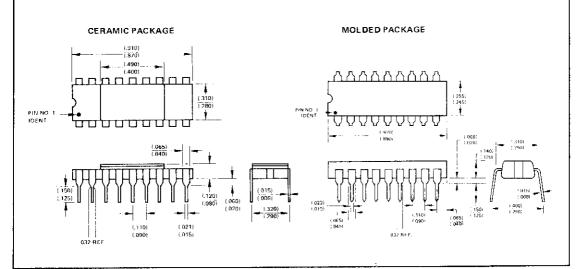

- 40 and 28 pin package versions

- Pipeline architecture

The SY6500 Series Microprocessors represent the first totally software compatible microprocessor family. This family of products includes a range of software compatible microprocessors which provide a selection of addressable memory range, interrupt input options and on-chip clock oscillators and drivers. All of the microprocessors in the SY6500 family are software compatible within the group and are bus compatible with the MC6800 product offering.

The family includes six microprocessors with on-board clock oscillators and drivers and four microprocessors driven by external clocks. The on-chip clock versions are aimed at high performance, low cost applications where single phase inputs or crystals provide the time base. The external clock versions are geared for the multi-processor system applications where maximum timing control is mandatory. All versions of the microprocessors are available in 1 MHz, 2 MHz, and 3 MHz maximum operating frequencies,

### MEMBERS OF THE FAMILY

| PART    | IUMBERS |          |      | l ;          |              |              |            |

|---------|---------|----------|------|--------------|--------------|--------------|------------|

| Plastic | Ceramic | CLOCKS   | PINS | ĪRQ          | NMI          | RDY          | ADDRESSING |

| SYP6502 | SYC6502 | On-Chip  | 40   | <b>√</b>     | √            |              | 16 (64 K)  |

| SYP6503 | SYC6503 | "        | 28   | ✓            | $\checkmark$ |              | 12 (4 K)   |

| SYP6504 | SYC6504 | "        | 28   | √            |              |              | 13 (8 K)   |

| SYP6505 | SYC6505 | **       | 28   | √            |              | $\checkmark$ | 12 (4 K)   |

| SYP6506 | SYC6506 | "        | 28   | <b>│</b>     |              |              | 12 (4 K)   |

| SYP6507 | SYC6507 | "        | 28   |              |              | √            | 13 (8 K)   |

| SYP6512 | SYC6512 | External | 40   | √            | $\checkmark$ | √            | 16 (64 K)  |

| SYP6513 | SYC6513 | 11       | 28   | ✓            | $\checkmark$ |              | 12 (4 K)   |

| SYP6514 | SYC6514 | 11       | 28   | <b> </b>     |              |              | 13 (8 K)   |

| SYP6515 | SYC6515 | "        | 28   | $\checkmark$ |              | $\checkmark$ | 12 (4 K)   |

### COMMENTS ON THE DATA SHEET

The data sheet is constructed to review first the basic "Common Characteristics" - those features which are common to the general family of microprocessors. Subsequent to a review of the family characteristics will be sections devoted to each member of the group with specific features of each.

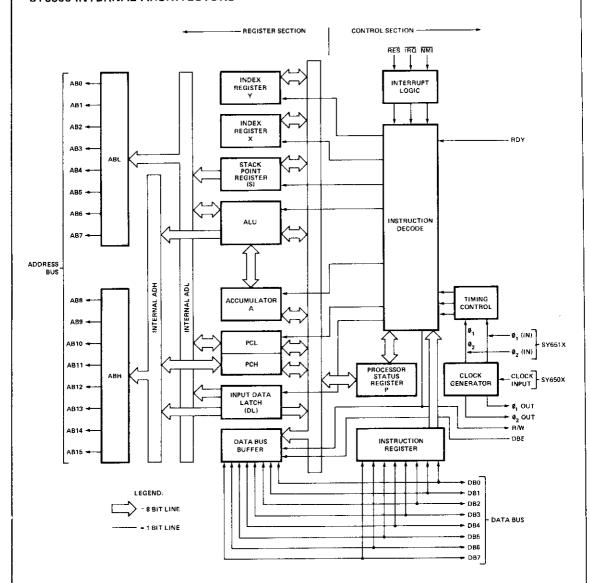

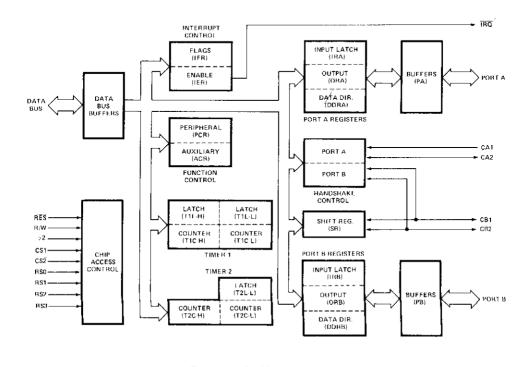

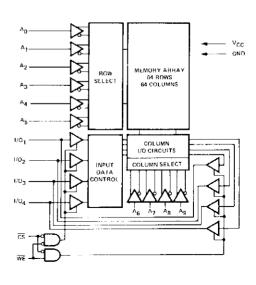

### SY6500 INTERNAL ARCHITECTURE

### NOTE:

CLOCK GENERATOR IS NOT INCLUDED ON SY651X.

ADDRESSING CAPABILITY AND CONTROL OPTIONS VARY WITH EACH OF THE SY6500 PRODUCTS.

### D.C. CHARACTERISTICS

### MAXIMUM RATINGS

| Rating                | Symbol           | Value        | Unit |

|-----------------------|------------------|--------------|------|

| Supply Voltage        | Vcc              | -0.3 to +7.0 | ٧    |

| Input Voltage         | Vin              | -0.3 to +7.0 | ٧    |

| Operating Temperature | TA               | 0 to +70     | °C   |

| Storage Temperature   | T <sub>STG</sub> | -55 to +150  | °C   |

### COMMENT

This device contains input protection against damage due to high static voltages or electric fields; however, precautions should be taken to avoid application of voltages higher than the maximum rating.

### **ELECTRICAL CHARACTERISTICS** ( $V_{CC} = 5.0V \pm 5\%$ , $T_A = 0-70^{\circ}C$ )

$(\emptyset_1, \emptyset_2 \text{ applies to SY651X}, \emptyset_{\alpha(in)} \text{ applies to SY650X})$

| Symbol              | Characteristic                                                      | Min.                  | Max.                   | Unit     |

|---------------------|---------------------------------------------------------------------|-----------------------|------------------------|----------|

| V <sub>IH</sub>     | Iπput High Voltage                                                  |                       |                        |          |

|                     | Logic, Ø <sub>o (in)</sub> (650X)                                   | +2.4                  | V <sub>cc</sub>        |          |

|                     | $\emptyset_1, \emptyset_2$ (651X)                                   | V <sub>cc</sub> - 0.5 | V <sub>cc</sub> + 0.25 | V        |

| V <sub>IL</sub>     | Input Low Voltage                                                   |                       |                        |          |

|                     | $Logic, \emptyset_{o(in)} $ (650X)                                  | -0.3                  | +0.4                   |          |

|                     | $\emptyset_1, \emptyset_2$ (651X)                                   | -0.3                  | +0.2                   | V        |

| !IL                 | Input Loading                                                       |                       |                        |          |

|                     | $(V_{in} = 0 \text{ V}, V_{cc} = 5.25 \text{ V})$                   | -10                   | -300                   | μΑ       |

|                     | RDY, S.O.                                                           |                       |                        |          |

| in                  | Input Leakage Current                                               |                       |                        |          |

|                     | $(V_{in} = 0 \text{ to } 5.25 \text{ V}, V_{cc} = 0)$               |                       |                        |          |

|                     | Logic (Excl. RDY, S.O.)                                             |                       | 2.5                    | μΑ       |

|                     | $\emptyset_1, \emptyset_2$ (651X)                                   | _                     | 100                    | μΑ       |

|                     | Ø <sub>o (in)</sub> (650X)                                          |                       | 10.0                   | μΑ       |

| TSI                 | Three-State (Off State) Input Current                               |                       |                        |          |

|                     | $(V_{in} = 0.4 \text{ to } 2.4 \text{ V}, V_{cc} = 5.25 \text{ V})$ |                       | 4.5                    |          |

|                     | DB0-DB7                                                             |                       | 10                     | μΑ       |

| V <sub>OH</sub>     | Output High Voltage                                                 |                       |                        |          |

| 1                   | $(I_{LOAD} = -100\mu Adc, V_{CC} = 4.75 \text{ V})$                 |                       |                        |          |

|                     | SYNC, DB0-DB7, A0-A15, R/W                                          | 2.4                   |                        | V        |

| V <sub>OL</sub>     | Output Low Voltage                                                  |                       |                        |          |

|                     | $(I_{LOAD} = 1.6 \text{mAdc}, V_{CC} = 4.75 \text{ V})$             |                       |                        |          |

| _                   | SYNC, DB0-DB7, A0-A15, R/W                                          |                       | 0.4                    | V        |

| P <sub>D</sub>      | Power Dissipation 1 MHz and 2 MHz                                   |                       | 700                    |          |

| l                   | 3 MHz                                                               |                       | 700<br>800             | mW<br>mW |

| С                   | Capacitance                                                         |                       | 000                    | 11190    |

|                     | $(V_{in} - 0, T_A = 25^{\circ}C, f = 1 MHz)$                        |                       |                        |          |

| C <sub>in</sub>     | "I RES, NMI, RDY, IRQ, S.O., DBE                                    |                       | 10                     |          |

| ) II                | DB0-DB7                                                             | _                     | 15                     |          |

| Cout                | A0-A15, R/W, SYNC                                                   |                       | 12                     | ρF       |

| Cout                | ·                                                                   | -                     |                        | •        |

| C <sub>Øo(in)</sub> | O(III)                                                              | _                     | 15                     |          |

| <sup>∨</sup> Ø₁     | Ø <sub>1</sub> (651X)                                               | _                     | 50                     |          |

| C <sub>Ø2</sub>     | Ø <sub>2</sub> (651X)                                               |                       | 80                     |          |

Note: IRQ and NMI require 3 K pull-up resistors.

### **DYNAMIC OPERATING CHARACTERISTICS**

$(V_{CC} = 5.0 \pm 5\%, T_A = 0^{\circ} \text{ to } 70^{\circ}\text{C})$

| Device |                                                       |              |                                 | 11                   | ИНz                           | 21       | ин z ⑥           | 31                   | инz 🤊            | T    |

|--------|-------------------------------------------------------|--------------|---------------------------------|----------------------|-------------------------------|----------|------------------|----------------------|------------------|------|

| Туре   | Parameter                                             | Note         | Symbol                          | Min.                 | Max.                          | Min.     | Max.             | Min.                 | Max.             | Unit |

|        | Cycle Time                                            |              | TCYC                            | 1.00                 | 40                            | 0.50     | 40               | 0.33                 | 40               | μs   |

|        | 0 <sub>1</sub> Pulse Width                            |              | TPWHØ1                          | 430                  |                               | 215      | _                | 150                  |                  | ns   |

| 651X   | 0 <sub>2</sub> Pulse Width                            | i            | T <sub>PWHØ2</sub>              | 470                  | _                             | 235      | _                | 160                  | _                | ns   |

|        | Delay Between 01 and 02                               |              | TD                              | 0                    | _                             | 0        |                  | 0                    |                  | ns   |

|        | 0 <sub>1</sub> and 0 <sub>2</sub> Rise and Fall Times | ①            | T <sub>R</sub> , T <sub>F</sub> | 0                    | 25                            | 0        | 20               | 0                    | 15               | ns   |

|        | Cycle Time                                            |              | TCYC                            | 1.00                 | 40                            | 0.50     | 40               | 0.33                 | 40               | μs   |

|        | Ø <sub>σ(IN)</sub> Low Time                           | 2            | TLØo                            | 480                  | _                             | 240      | _                | 160                  | -                | ns   |

|        | Ø <sub>o(IN)</sub> High Time                          | ②            | THØo                            | 460                  | i –                           | 240      | -                | 160                  | _                | ns   |

|        | Ø <sub>O</sub> Neg to Ø₁ Pos Delay                    | (5)          | T <sub>01+</sub>                | 10                   | 70                            | 10       | 70               | 10                   | 70               | ns   |

|        | 0 <sub>o</sub> Neg to 0 <sub>2</sub> Neg Delay        | <b>⑤</b>     | T <sub>02</sub> _               | 5                    | 65                            | 5        | 65               | 5                    | 65               | ns   |

| 650X   | On Pos to On Neg Delay                                | <b>⑤</b>     | 701~                            | 5                    | 65                            | 5        | 65               | 5                    | 65               | ns   |

|        | 0 <sub>0</sub> Pos to 0 <sub>2</sub> Pos Delay        | <b>06666</b> | T <sub>02+</sub>                | 15                   | 75                            | 15       | 75               | 15                   | 75               | ns   |

|        | 0 <sub>o(IN)</sub> Rise and Fall Time                 | ①            | TRO, TFO                        | 0                    | 10                            | 0        | 10               | 0                    | 10               | ns   |

|        | 01(OUT) Pulse Width                                   |              | T <sub>PWHØ1</sub>              | TLØ <sub>0</sub> -20 | T <sub>L</sub> Ø <sub>Q</sub> | TL00-20  | T <sub>LØo</sub> | TLØ <sub>0</sub> -20 | T∟Ø <sub>O</sub> | ns   |

|        | 02(OUT) Pulse Width                                   |              | T <sub>PWHØ2</sub>              | TLØ0-40              | TLØ 10                        | TL 00-40 | TLØ0-10          | TL00-40              | TLØ0-10          | nş.  |

|        | Delay Between 0 <sub>1</sub> and 0 <sub>2</sub>       |              | T <sub>D</sub> *                | 5                    |                               | 5        | -                | 5                    | _                | កន   |

|        | $\emptyset_1$ and $\emptyset_2$ Rise and Fall Times   | ①③           | TR, TF                          | -                    | 25                            | -        | 25               | _                    | 15               | ns   |

|        | R/W Setup Time                                        |              | TRWS                            | -                    | 225                           | -        | 140              |                      | 110              | ns   |

|        | R/W Hold Time                                         |              | TRWH                            | 30                   | -                             | 30       | _                | 15                   | - '              | ns   |

|        | Address Setup Time                                    |              | TADS                            | -                    | 225                           | -        | 140              |                      | 110              | ns   |

|        | Address Hold Time                                     |              | TADH                            | 30                   | - ,                           | 30       | _                | 15                   | -                | ns   |

| 1      | Read Access Time                                      |              | TACC                            | _                    | 650                           |          | 310              | -                    | 170              | ns   |

| 650X   | Read Data Setup Time                                  |              | TDSU                            | 100                  | -                             | 50       | _                | 50                   | _                | ns   |

| 651X   | Read Data Hold Time                                   |              | THR                             | 10                   |                               | 10       | _                | 10                   | _                | ns   |

|        | Write Data Setup Time                                 | 1            | TMDS                            | - 1                  | 175                           | -        | 100              | _                    | 75               | ns   |

|        | Write Data Hold Time                                  |              | THW                             | 60                   | -                             | 60       |                  | 30                   | -                | ns   |

|        | Sync Setup Time                                       |              | TSYS                            | -                    | 350                           | _        | 175              | _                    | 100              | ns   |

|        | Sync Hold Time                                        |              | TSYH                            | 30                   | -                             | 30       | -                | 15                   | _                | ns   |

|        | RDY Setup Time                                        | <b>④</b>     | TRS                             | 200                  | -                             | 200      |                  | 150                  | _                | ns   |

### NOTES:

- Measured between 10% and 90% points on waveform.

- Measured at 50% points.

- 3 Load = 1 TTL load +30 pF.

- RDY must never switch states within  $T_{RS}$  to end of  $\theta_2$ .

- 5 Load = 100 pF.

- The 2 MHz devices are identified by an "A" suffix.

- The 3 MHz devices are identified by a "B" suffix.

#### PIN FUNCTIONS

### Clocks (0, , 0,)

The SY651X requires a two phase non-overlapping clock that runs at the  $V_{\rm CC}$  voltage level.

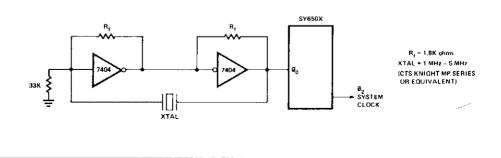

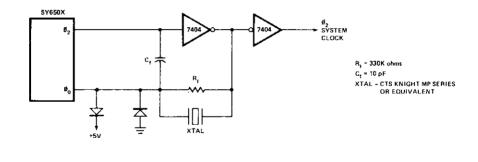

The SY650X clocks are supplied with an internal clock generator. The frequency of these clocks is externally controlled. Clock generator circuits are shown elsewhere in this data sheet.

Address Bus  $(A_0\cdot A_{15})$  (See sections on each micro for respective address lines on those devices.)

These outputs are TTL compatible, capable of driving one standard TTL load and 130 pF.

### Data Bus (DB<sub>0</sub>-DB<sub>7</sub>)

Eight pins are used for the data bus. This is a bi-directional bus, transferring data to and from the device and peripherals. The outputs are three-state buffers, capable of driving one standard TTL load and 130 pF.

#### Data Bus Enable (DBE)

This TTL compatible input allows external control of the three-state data output buffers and will enable the microprocessor bus driver when in the high state. In normal operation DBE would be driven by the phase two  $\{\emptyset_2\}$  clock, thus allowing data output from microprocessor only during  $\emptyset_2$ . During the read cycle, the data bus drivers are internally disabled, becoming essentially an open circuit. To disable data bus drivers externally, DBE should be held low. This signal is available on the SY6512, only.

#### Ready (RDY)

This input signal allows the user to halt the microprocessor on all cycles except write cycles. A negative transition to the low state during or coincident with phase one  $(\emptyset_1)$  will halt the microprocessor with the output address lines reflecting the current address being fetched. This condition will remain through a subsequent phase two  $(\emptyset_2)$  in which the Ready signal is low. This feature allows microprocessor interfacing with low speed PROMS as well as fast (max. 2 cycle) Direct Memory Access (DMA). If ready is low during a write cycle, it is ignored until the following read operation. Ready transitions must not be permitted during  $\emptyset_2$  time.

### Interrupt Request (IRQ)

This TTL level input requests that an interrupt sequence begin within the microprocessor. The microprocessor will complete the current instruction being executed before recognizing the request. At that time, the interrupt mask bit in the Status Code Register will be examined. If the interrupt mask flag is not set, the microprocessor will begin an interrupt sequence. The Program Counter and Processor Status Register are stored in the stack. The microprocessor will then set the interrupt mask flag high so that no further interrupts may occur. At the end of this cycle, the program counter low will be loaded from address FFFE, and program counter high from location FFFF, therefore transferring program control to the memory vector located at these addresses. The RDY signal must be in the high state for any interrupt to be recognized. A  $3K\Omega$  external resistor should be used for proper wire-OR operation.

### Non-Maskable Interrupt (NMI)

A negative going transition on this input requests that a non-maskable interrupt sequence be generated within the microprocessor.

NMI is an unconditional interrupt. Following completion of the current instruction, the sequence of operations defined for IRQ will be performed, regardless of the state interrupt mask flag. The vestor address loaded into the program counter, low and high, are locations FFFA and FFFB respectively, thereby transferring program control to the memory vector located at these addresses. The instructions loaded at these locations cause the microprocessor to branch to a non-maskable interrupt routine in memory.

$\overline{\text{NMi}}$  also requires an external  $3K\Omega$  resistor to  $V_{CC}$  for proper wire-OR operations.

Inputs  $\overline{\text{IRQ}}$  and  $\overline{\text{NMI}}$  are hardware interrupts lines that are sampled during  $\emptyset_2$  (phase 2) and will begin the appropriate interrupt routine on the  $\emptyset_1$  (phase 1) following the completion of the current instruction.

#### Set Overflow Flag (S.O.)

A NEGATIVE going edge on this input sets the overflow bit in the Status Code Register. This signal is sampled on the trailing edge of  $Q_1$ .

#### SYNC

This output fine is provided to identify those cycles in which the microprocessor is doing an OP CODE fetch. The SYNC line goes high during  $\emptyset_1$  of an OP CODE fetch and stays high for the remainder of that cycle. If the RDY line is pulled low during the  $\emptyset_1$  clock pulse in which SYNC went high, the processor will stop in its current state and will remain in the state until the RDY line goes high. In this manner, the SYNC signal can be used to control RDY to cause single instruction execution.

#### Reset (RES)

This input is used to reset or start the microprocessor from a power down condition. During the time that this line is held low, writing to or from the microprocessor is inhibited. When a positive edge is detected on the input, the microprocessor will immediately begin the reset sequence.

After a system initialization time of six clock cycles, the mask interrupt flag will be set and the microprocessor will load the program counter from the memory vector locations FFFC and FFFD. This is the start location for program control

After  $V_{\rm CC}$  reaches 4.75 volts in a power up routine, reset must be held low for at least two clock cycles. At this time the R/W and SYNC signal will become valid.

When the reset signal goes high following these two clock cycles, the microprocessor will proceed with the normal reset procedure detailed above.

#### Read/Write (R/W)

This output signal is used to control the direction of data transfers between the processor and other circuits on the data bus. A high level on R/W signifies data into the processor; a low is for data transfer out of the processor.

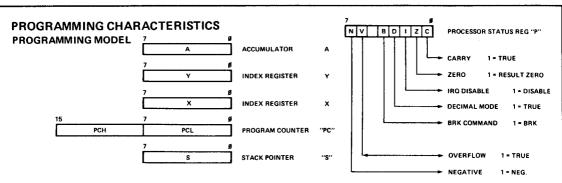

## PROGRAMMING CHARACTERISTICS INSTRUCTION SET – ALPHABETIC SEQUENCE

| ADC | Add Memory to Accumulator with Carry       | DEC | Decrement Memory by One                     | PHA  | Push Accumulator on Stack                    |

|-----|--------------------------------------------|-----|---------------------------------------------|------|----------------------------------------------|

| AND | "AND" Memory with Accumulator              | DEX | Decrement Index X by One                    | PHP  | Push Processor Status on Stack               |

| ASL | Shift left One Bit (Memory or Accumulator) | DEY | Decrement Index Y by One                    | PLA  | Pull Accumulator from Stack                  |

|     |                                            |     |                                             | PLP  | Pull Processor Status from Stack             |

| BCC | Branch on Carry Clear                      | FOR | "Exclusive or" Memory with Accumulator      |      |                                              |

| BCS | Branch on Carry Set                        |     |                                             | RQL  | Rotate One Bit Left (Memory or Accumulator)  |

| BEQ | Branch on Result Zero                      | INC | Increment Memory by One                     | ROR  | Rotate One Bit Right IMemory or Accumulator) |

| BIT | Test Bits in Memory with Accumulator       | INX | Increment Index X by One                    | RTI  | Return from Interrupt                        |

| BMI | Branch on Result Minus                     | INY | Increment Index Y by One                    | RTS  | Return from Subroutine                       |

| BNE | Branch on Result not Zero                  |     |                                             |      |                                              |

| BPL | Branch on Result Plus                      | JMP | Jump to New Location                        | SBC  | Subtract Memory from Accumulator with Borrow |

| BAK | Force Break                                | JSR | Jump to New Location Saving Return Address  | SEC  | Set Carry Flag                               |

| BVC | Branch on Overflow Clear                   |     |                                             | SED  | Set Decimal Mode                             |

| BVS | Branch on Overflow Set                     | LŪA | Load Accumulator with Memory                | SE1  | Set Interupt Disable Status                  |

|     |                                            | LDX | Load Index X with Memory                    | STA  | Store Accumulator in Memory                  |

| CLC | Clear Carry Flag                           | LDY | Load Index Y with Memory                    | STX  | Store Index X in Memory                      |

| CLD | Clear Decimal Mode                         | LSR | Shift One Bit Right (Memory or Accumulator) | STY  | Stare Index Y in Memory                      |

| CLI | Clear Interrupt Disable Bit                |     |                                             |      |                                              |

| CLV | Clear Overflow Flag                        | NOP | No Operation                                | TAX  | Fransfer Accumulator to Index X              |

| CMP | Compare Memory and Accumulator             |     |                                             | YAI  | Transfer Accumulator to Index Y              |

| CPX | Compare Memory and Index X                 | ORA | "OR" Memory with Accumulator                | T\$X | Transfer Stack Pointer to Index X            |

| CPY | Compare Memory and Index Y                 |     |                                             | TXA  | Transfer Index X to Accumulator              |

|     |                                            |     |                                             | TXS  | Transfer Index X to Stack Pointer            |

|     |                                            |     |                                             | TYA  | Transfer Index Y to Accumulator              |

#### **ADDRESSING MODES**

### **Accumulator Addressing**

This form of addressing is represented with a one byte instruction, implying an operation on the accumulator.

### Immediate Addressing

In immediate addressing, the operand is contained in the second byte of the instruction, with no further memory addressing required.

### Absolute Addressing

In absolute addressing, the second byte of the instruction specifies the eight low order bits of the effective address while the third byte specifies the eight high order bits. Thus, the absolute addressing mode allows access to the entire 65K bytes of addressable memory.

#### Zero Page Addressing

The zero page instructions allow for shorter code and execution times by only fetching the second byte of the instruction and assuming a zero high address byte. Careful use of the zero page can result in significant increase in code efficiency.

### Indexed Zero Page Addressing - (X, Y indexing)

This form of addressing is used in conjunction with the index register and is referred to as "Zero Page, X" or "Zero Page, Y." The effective address is calcuated by adding the second byte to the contents of the index register. Since this is a form of "Zero Page" addressing, the content of the second byte references a location in page zero. Additionally due to the "Zero Page" addressing nature of this mode, no carry is added to the high order 8 bits of memory and crossing of page boundaries does not occur.

### Indexed Absolute Addressing - (X, Y indexing)

This form of addressing is used in conjunction with X and Y index register and is referred to as "Absolute, X," and "Absolute, Y." The effective address is formed by adding the contents of X or Y to the address contained in the second and third bytes of the instruction. This mode allows the index register to contain the index or count value and the instruction to contain the base address. This type of indexing allows any location referencing and the index to modify multiple fields resulting in reduced coding and execution time.

### Implied Addressing

In the implied addressing mode, the address containing the operand is implicitly stated in the operation code of the instruction.

#### Relative Addressing

Relative addressing is used only with branch instructions and establishes a destination for the conditional branch.

The second byte of the instruction becomes the operand which is an "Offset" added to the contents of the lower eight bits of the program counter when the counter is set at the next instruction. The range of the offset is -128 to +127 bytes from the next instruction.

#### Indexed Indirect Addressing

In indexed indirect addressing (referred to as (Indirect,X)), the second byte of the instruction is added to the contents of the X index register, discarding the carry. The result of this addition points to a memory location on page zero whose contents is the low order eight bits of the effective address. The next memory location in page zero contains the high order eight bits of the effective address. Both memory locations specifying the high and low order bytes of the effective address must be in page zero.

### Indirect Indexed Addressing

In indirect indexed addressing (referred to as (Indirect),Y), the second byte of the instruction points to a memory location in page zero. The contents of this memory location is added to the contents of the Y index register, the result being the low order eight bits of the effective address. The carry from this addition is added to the contents of the next page zero memory location, the result being the high order eight bits of the effective address.

### Absolute Indirect

The second byte of the instruction contains the low order eight bits of a memory location. The high order eight bits of that memory location is contained in the third byte of the instruction. The contents of the fully specified memory location is the low order byte of the effective address. The next memory location contains the high order byte of the effective address which is loaded into the sixteen bits of the program counter.

### INSTRUCTION SET - OP CODES, EXECUTION TIME, MEMORY REQUIREMENTS

|         | METRUCTIONS           | ſ  |    | EOI | 116 | •  | 050 | K D1 |     | 26 | 80 4 | 461 | Г   | ACC | , | Г   | •   | 40 | Г   | (180 | ¥)  | Γ  | IIHO  | C.Y | 1  | PA |         | Γ    | 485     | ¥ . | L  | ASI     | ٧  | L   | e i a i | ivi | 149 | DIRE | c r | 1       | PAG | į į     | l  | (        | 940 | 1710 | ) <b>4</b> C | :00 | "   |     |

|---------|-----------------------|----|----|-----|-----|----|-----|------|-----|----|------|-----|-----|-----|---|-----|-----|----|-----|------|-----|----|-------|-----|----|----|---------|------|---------|-----|----|---------|----|-----|---------|-----|-----|------|-----|---------|-----|---------|----|----------|-----|------|--------------|-----|-----|-----|

| REFRORK | OPE RATION            | 1  | ٥P | Ŋ   | *   | 0  | P   | N    |     | OP | N    |     | OF  | N   | - | o   | N   | T  | or  | N    |     | OF | N     | -   | OF | N  | ŀ       | ŀloi | PN      |     | O  | P       | Ţ  | ŀ   | N       |     | OР  | N    |     | O       | PN  | Ŀ       | ŀ  |          | Z   | ç    | 1            | Ç   | _   | v   |

| ADC     | A+M+C-A (4)(1         | 11 | 69 | 2   | 2   | 6  | o   | 4    | 3   | 65 | 3    | 2   | Ī   | Т   | Т | Г   | Ţ   | Т  | 61  | 6    | 2   | 71 | 5     | 2   | 75 | 14 | T2      | 70   | 1       | 3   | 79 | 4       | 13 | T   | Τ       | Τ   | Γ   | Τ    | Γ   | 1       | T   | T       | 1  |          | ,   | ,    | -            | -   | -   | ,   |

| AND     | A A M → A U           | 1) | 29 | 2   | 2   | 2  | ο   | 4    | 3   | 25 | 3    | 2   |     |     | 1 |     |     | ı  | 21  | 6    | 2   | 31 | 5     | 2   | 35 | 4  | 2       | 30   | 4       | 3   | 39 | 4       | 3  | 1   |         | 1   |     | ł    |     | ı       | i.  | 1       | 1, | ,        | ,   | -    | -            | -   |     | -   |

| ASL     | C ◀ 7 0 ◀ 8           | ١  |    |     |     | 9  | €   | 6    | 3   | #6 | 5    | 2   | 9 4 | 2   | 1 | ŀ   | 1   | i. | l   | 1    | ı   | 1  | 1     | 1   | 16 | 6  | 2       | 11   | E 7     | 3   | ı  |         | 1  |     |         | 1   | ļ   | ı    |     | ı       |     | 1       | 1, |          | ,   | ı    | -            | -   | -   | -   |

| BCC     | BRANCH ON C-6 (2      | 2) |    |     |     | ı  |     |      | - 1 |    |      |     |     | 1   |   | 1   | 1   | 1  | 1   | 1    | i   | 1  | -     | į . |    | 1  | 1       | ı    | 1       | 1   | ı  |         |    | 96  | 2       | 2   |     | ı    | 1   | ı       |     | 1       | ۱- |          | -   | -    | -            | -   | -   | -   |

| BCS     | BRANCH ON C=1 (2      | 2) |    |     | l   | ı  | -   | 1    |     |    |      |     | l   | ì   |   | ŀ   | 1   | 1  | ĺ   |      | ļ   | l  |       | 1   |    | 1  |         | 1    |         |     | ı  |         | 1  |     | 9 2     |     |     | L    | L   |         |     |         | Ŀ  |          | -   | -    |              | -   | _   | - ] |

| BEQ     | BRANCH ON Z=1 (2      | 2) |    | _   | 1   | Г  | 7   |      |     |    | 1    | T   |     | Т   | Т | Т   | Т   | Т  | Г   | 1    | Г   | T  | T     | T   | 1  | Τ  | Т       | Т    | T       | Τ   | T  | Т       | Т  | F   | 2       | 2   | T   | Г    | Т   | Г       | Т   | T       | Ţ- |          | -   | ~    | -            | -   |     | - ] |

| BIT     | AAM                   | 1  |    |     | i   | 2  | c   | 4    | 3   | 24 | 3    | 2   |     |     |   | 1   | 1   |    | ļ   |      | ı   | l  |       | 1   |    | 1  |         | 1    | 1       | 1   | į. | i.      | 1  | 1   |         | 1   | 1   | ı    |     | ı       |     | 1       | 1м | ١, ،     | ,   | -    | -            | -   | ٠ ٨ | ۸,  |

| вмі     | BRANCH ON N=1 (2      | 20 |    |     | l   | 1  |     |      | ١   |    | 1    |     |     |     |   | ı   |     |    | ı   |      | !   | l  | 1     | Ì   | l  | 1  |         | ı    | 1       |     | 1  | İ       | 1  | 30  | 2       | 2   | ł   | ı    |     |         |     | 1       | -  |          | -   | -    | -            | -   | -   | - ! |

| BNE     | BRANCH ON Z=9 12      | 21 |    |     | ı   | ı  |     |      |     |    | 1    |     | ł   |     |   | ı   |     | 1  | ļ   |      | 1   | l  |       |     | 1  | 1  | 1       |      |         |     | 1  | 1       |    | D   | 3 2     | 2   | 1   | ı    | İ   | 1       |     |         | 1- |          | -   | -    | -            | -   |     | - ! |

| BPL     | BRANCH ON N=9 12      | 21 |    |     |     | l  |     | ł    | 1   |    |      | 1   | 1   |     | İ | 1   |     |    | 1   | 1    | i   | i  | 1     | ì   | 1  |    |         | 1    | 1       | 1   | 1  |         |    | 156 | 1 2     | 2   | 1   | L    |     | 1       |     | L       | -  |          | -   | -    | -            | -   | -   | - j |

| BRK     | (See Fig. 1)          | Ť  |    | Г   | Γ   | Г  | T   | 7    |     |    | T    | T   | Г   | T   | T | 94  | 7   | 1  | Г   | T    | Т   |    | Т     | T   |    | T  | T       | T    | Т       | Т   | Т  | T       | Т  | Т   | Т       | Ţ   | Г   | Г    | Т   | Γ       | T   | Т       | T- |          | -   | -    | -            | -   | -   | -7  |

| вис     | BRANCH ON V-9 12      | 21 |    |     |     | ı  |     | - 1  | 1   |    |      |     |     | 1   | ł | ı   | -   | 1  | l   | İ    |     |    | 1     |     | 1  |    |         | 1    | 1       |     | ı  | 1       | i  | 56  | 2       | 2   | 1   | ı    | 1   | 1       |     |         | -  |          | -   | -    | -            |     |     | - 1 |

| BVS     | BRANCH ON V+1 12      | 2) |    |     |     |    |     | -    | 1   |    |      |     |     |     |   | 1   |     |    |     |      |     |    |       | i   |    |    |         | 1    |         |     | ı  |         | 1  | 70  | 2       | 2   | t   | ı    |     |         |     | 1       | -  |          | -   | -    | -            | -   | -   | -   |

| CLC     | 0 - C                 | 1  |    |     | 1   |    |     | ı    | -   |    |      | 1   | 1   |     | ļ | 116 | 2   | 1  | l   | ı    | 1   | ı  | 1     | 1   |    |    |         | 1    |         | 1   | L  |         |    |     |         | 1   | ł   | ı    | 1   | 1       | 1   | 1       | 1- |          | -   | 0    | -            | -   | -   | -   |

| CLD     | 0 - D                 | 1  |    | Ĺ_  |     | L  | 1   | _    |     |    |      |     | L   |     |   | 08  | 3 2 | 1  | L   | L    | L   | L. |       |     |    | I. | 1       | L    | 1.      | Ĺ.  | L  | L       | ┸  | L   | ┸       | L   | L   | L    | L   | L       | ⊥.  | ┸       | Ŀ  |          |     | -    | -            |     | _   |     |

| CLI     | <b>0</b> → 1          | I  |    |     |     | I  | -   | -1   | ı   |    |      | 1   | ı   |     |   | 58  | 3 2 | 1  | •   |      | I   | I  | İ     |     |    |    | İ       | 1    |         |     | I  | Ţ       | 1  | 1   |         | 1   | 1   | i.   | 1   | ı       | ł   |         | 1- |          | -   | -    |              | -   | -   | -   |

| CLV     | <b>0</b> → ∨          | 1  |    |     |     |    | -   | -    |     |    |      | 1   | 1   |     |   | BE  | 3 2 | 1  |     | ĺ    |     | l  |       | 1   | l  |    | 1       | 1    | i       |     | 1  | 1       | 1  | 1   |         |     | ı   | ı    | 1   | ı       | 1   |         | 1- |          | -   | -    | -            | -   | - 1 | 9   |

| CMP     | A-M (1                |    |    |     |     |    |     |      |     | C5 |      |     |     |     |   | 1   | -   |    | C   | 6    | 2   | DI | 1   5 | 2   | D  | 4  | 2       | DO   | D 4     | 3   | DS | 9 4     | 3  | 1   |         |     | 1   | ı    |     | l       |     | 1       | 1  | ٠.       | •   | 1    |              | -   | -   | -   |

| CPX     | X-M                   |    |    |     |     |    |     |      |     | E4 |      |     |     |     |   |     | 1   |    | ı   |      | ŀ   | 1  | 1     | 1   |    |    | -       | ı    |         |     | 1  |         |    | 1   |         |     | ı   | ł    |     | 1       | 1   |         | 1  |          | ,   | ı    | -            | -   |     | -   |

| CPY     | Y-M                   | 4  | C9 | 2   | 2   |    |     |      |     | C4 |      |     |     | L   | L | 1_  | L   | 1  | L., | L    | L   | L  | 1     | L   | L  | 1  | $\perp$ | L    | $\perp$ | L   | L  | $\perp$ | 1  | ┸   | 1       | L   | ┖   | L    | L   | <u></u> | 1.  | 1       | 1  | '        | _   | 1    |              |     |     | -   |

| DEC     | M-1 → M               | 1  |    |     | l   | c  | E   | 6    | 3   | C6 | 5    | 2   | 1   |     |   |     |     |    | ı   |      | ı   |    |       | 1   | D€ | 6  | 2       | P    | E 7     | 3   | L  |         |    | 1   | 1       |     | ı   | 1    |     | ı       | 1   |         | 1  | ٠.       | -   | -    | TMT          | -   |     | -   |

| DEX     | X-1 - X               | 1  |    |     | ĺ   | ı  | -   | ı    | ı   |    |      |     | 1   |     | 1 | C   | 1.  | 1  | ı   |      | i . |    |       | 1   |    |    |         | ı    |         | 1   | ı  |         |    | 1   | 1       | 1   | ı   |      |     | ı       | 1   | 1       | 1  | ٠.       | 1   | -    | -            | -   |     | - 1 |

| DEY     | Y-1 - Y               | 1  |    |     |     | ŀ  |     |      |     |    |      | 1   | 1   |     |   | 88  | 2   | ١  | ı   |      | ı   | ı  | 1     | 1   | ı  | 1  | ļ       | ı    | 1       |     | ı  |         |    | i.  |         | Ĺ   | ı   | ļ    | 1   | ı       |     | ì       | 1  | ′ .      | /   | -    | -            |     |     | - 1 |

| EOR     |                       | 바  | 49 | 2   |     |    |     |      |     | 45 |      |     |     |     |   |     | 1   |    | 41  | 6    | 2   | 51 | 5     | 2   |    |    |         |      | 4       |     |    | 9 4     | 13 | 1   |         |     | 1   |      | 1   | ı       | ı   |         | 1  | ٠.       | 1   | -    | ~            | -   | •   | - } |

| INC     | M + 1 → M             | 1  |    | L   | Ļ.  | E  | E   | 6    | 3   | E6 | 5    | 2   | 1_  | ļ., | Ļ | ⇂   | 1   | ┸  | ┖   | ╀    | ┖   | ┖  | ╀     | ┺   | FE | 6  | 2       | F    | 5 7     | 3   | ↓_ | 4       | 1  | 1   | 1       | ╀   | ↓_  | L    | L   | ┺       | 4   | +       | ľ  | <u>_</u> | _   | -    |              | _   | _   | _   |

| INX     | X + 1 - X             | 1  |    |     |     |    |     |      | ١   |    |      |     | 1   | i   | İ |     |     | 1  | ı   |      |     |    | 1     | 1   | ı  | 1  |         | 1    | 1       | İ   | 1  |         |    | 1   |         | 1   | ı   |      |     |         | 1   | İ       | 1  |          | /   |      | ~            | -   | -   | -   |

| INY     | Y + 1 - Y             | 1  |    |     |     |    | Ì   |      | ١   |    | İ    |     | 1   | -   |   | CE  | 3 2 | 1  | ı   |      |     |    | 1     | 1   | 1  | 1  |         | ĺ    |         |     | ı  |         | 1  | 1   |         | 1   | 1   |      |     | i       | 1   | 1       | 1  | ٠.       | /   | -    | -            | -   |     | -   |

| JMP     | JUMP TO NEW LOC       | 1  |    |     |     |    |     | 3    |     |    |      | 1   | 1   |     |   |     |     | 1  | ı   |      |     | 1  | 1     | 1   | l  | 1  |         | 1    |         | 1   | ı  | 1       | 1  | 1   |         |     | 60  | 5    | 3   | 1       | 1   |         | 1. |          | -   | -    | -            | -   |     | - } |

| 12 H    | (See Fig. 2) JUMP SUB | 1  |    |     |     |    | 0   |      | 3   |    |      |     | İ   |     |   | 1   |     | ì  |     | 1    |     | 1  |       |     | ı  | Ì  |         | 1    |         |     | ı  |         |    | 1   |         | 1   | I   |      | 1   |         | 1   |         | 1- |          | -   | -    | -            | -   |     | -   |

| LOA     | M - A (1              | υĮ | 49 | 2   | [2  | ļ۵ | D   | 4    | 3   | Α5 | 3    | 2   | L   | L   | L | L   | L   | L  | Δı  | 6    | 2   | 81 | 5     | 2   | 85 | 4  | 12      | 80   | 9       | 3   | 89 | 4       | 13 | Ł   | L       | L   | L   | L    | L   | L       | L   | $\perp$ | Ľ  | _        | ′   | -    | _            | _   |     | - / |

|        |                                |      | H PL | 171  | 444        | 10 k H | 76  | ZE  | RQ 7. | A66. |     | ACCI | - | Т  | -   | 160 | T   | (10) | , <b>1</b> 0 | Т   | #40 | ), Y | 2   | PAG          | 4.1 | 1   | 46. |    | Г  | 455 |   | Ţ. | ELAT | IVE | -  | 91R | eet | T   | Z, PA | 18E. | 7  |     | C D B | DIT | 01  | coo | es |     |

|--------|--------------------------------|------|------|------|------------|--------|-----|-----|-------|------|-----|------|---|----|-----|-----|-----|------|--------------|-----|-----|------|-----|--------------|-----|-----|-----|----|----|-----|---|----|------|-----|----|-----|-----|-----|-------|------|----|-----|-------|-----|-----|-----|----|-----|

| меновк | SPERATION.                     |      |      |      |            |        |     | OP  |       |      |     | N    |   | 0  | PN  |     | 01  | PN   | *            | Of  | N   | *    | OF  | N            |     | OF  | N   |    | 0  | N   |   | o  | N    | *   | 01 | P   | ıŢ, | . 0 | P     | N    | *  | N   | z     | С   |     | Г   | Б_ | V   |

| LDX    | M → X (1)                      | A2   |      |      |            |        |     |     |       |      |     | T    | T | T  | 1   | 1   | Ī   | 1    | Τ            |     | T   | Г    |     | T            | Т   | Т   | T   |    | В  |     |   |    | Т    | T   | T  | T   | T   |     | 36    |      |    | 7   | 7     | -   | _   |     | -  | 7   |

| LDY    | M Y (1)                        | AØ   | 2    | 2    | AC         | 4      | 3   | A4  | 3     | 2    | l   |      | ł | l  | П   |     |     |      | 1            | 1   |     |      | 84  | 4            | 2   | ВС  | 4   | 3  | ı  | 1   | i | ı  |      |     |    | ı   | ı   | ı   |       |      | -1 | 4   | 1     | -   | -   | ٠.  | -  | -   |

| LSR    | <b>9→</b> 7 0 → C              | ı    |      |      | 4E         | 6      | 3   | 46  | 5     | 2    | 4 A | 2    | 1 | ı  | ı   |     |     | П    |              | ı   |     |      | 56  | 6            | 2   | 5€  | 7   | 3  | ı  |     | 1 | ı  |      |     | l  |     | ı   | 1   | -     | - 1  | -1 |     | ∢     | 4   | -   |     | -  | -1  |

| NOP    | NO OPERATION                   | ı    | 1    |      |            |        |     | ĺ   |       |      | l   | l    |   | E  | 4 2 | ١,  |     |      |              | 1   |     |      | ı   |              |     | ı   | 1   | ì  | ı  |     |   | i  |      |     |    |     | ı   | 1   | - 1   | -    | -1 | -   | -     | -   | -   |     | -  | -1  |

| ARO    | AVM+A                          | 99   | 2    | 2    | <b>⊕</b> D | 4      | 3   | 95  | 3     | 2    | l   | 1    | ł |    | П   |     |     | 1 6  | 2            | 111 | 5   | 2    | 15  | 4            | 2   | 10  | 4   | 3  | 15 | 4   | 3 | l  | ı    | l.  | l  | 1   | l   | 1   | 1     | . 1  |    | 1   | •     | -   | -   |     | -  | -   |

| PHA    | A → Ms S-1 → S                 |      | T    | Г    | Г          |        | Г   |     | Γ     | Γ    | Г   | Т    | Τ | 41 | 3 3 | 1   | Γ   | Т    | F            | П   | Τ   | Г    | Ι   | Т            | Г   | Γ   | Т   | Г  | Γ  | Т   | Τ | Γ  | Т    | Γ   | Г  | T   | Т   | T   | T     |      | Ī  | -   | -     | -   | -   |     | -  | -   |

| PHP    | P Ms S-1 S                     |      |      |      |            | 1      | ļ   | 1   | -     |      | ı   | 1    |   | 91 | 3 3 | 1   |     |      |              | ı   |     | ļ    |     |              |     | ı   |     |    | ı  |     |   | l  | 1    |     |    | 1   | l   |     |       | 1    | -  | -   | -     | -   | -   |     | -  | -   |

| PLA    | S + 1 - S Ms - A               |      | 1    |      |            | l      |     |     | 1     |      | l   | 1    | 1 | 61 | 3 4 | ١   | l   |      |              | ı   | 1   | 1    |     |              |     | 1   |     |    |    |     | İ |    | 1    |     |    |     | i   |     | 1     |      | 1  | ٧   | J     | -   | -   |     |    | -1  |

| PLP    | S+1→S Mi→P                     | 1    | 1    | i    |            |        |     |     | 1     |      | l   |      | ļ | 21 | 3 4 | ١,  | ļ   |      |              | ı   |     | 1    | 1   |              |     | ł   | ł   |    | ı  |     |   | İ  | 1    |     |    |     | ł   |     |       |      | -1 |     | R     | ES1 | (0) | RE  | D) | -   |

| ROL    | <b>√</b> 0 <b>√</b> C <b>√</b> | L    |      |      |            |        |     | 26  |       |      |     |      |   |    |     | L   | 1   | L    |              | L   | L   |      |     |              |     | 36  |     |    |    | L   |   | L  |      |     | L  | l   | L   | L   |       | ┙    | ┙  | Į   | 4     | 1   |     | _   | -  | -   |

| ROR    | <b>→ c → 7 d→</b>              |      | Γ    |      | 6E         | 6      | 3   | 66  | 5     | 2    | 6A  | 2    | 1 |    |     |     |     | 1    |              | ı   |     | I    | 76  | 6            | 2   | 76  | į   | 3  | ı  | Ī   | Ī |    |      | ĺ   |    | ı   | 1   | 1   | - [   |      | -  |     |       | 4   |     |     |    | -1  |

| RTI    | (See Fig. 1) RTRN INT.         |      |      |      |            |        | l   |     |       |      | l   |      | 1 |    | 6   |     | ŀ   |      |              | !   |     | ļ    | ł   |              | l   |     | l   |    | 1  | i   |   | ĺ  | 1    |     |    |     | 1   | 1   |       | -    | .  |     | RE    | ST  | OF  | ₹EI | D١ |     |

| RTS    | (See Fig. 2) ATRN SUB          |      |      |      |            |        |     |     |       |      | l   |      | 1 | 64 | 6   | 1   |     | İ    |              | ı   |     | į    | 1   |              |     |     |     |    |    | l   | Ì |    |      | ł   | 1  |     | ı   | 1   | - [   | ľ    | 1  | -   | -     | -   | -   |     | -  | -   |

| SBC    | A-M-C → A (1)                  | E9   | 2    | 2    | ΕĐ         | 4      | 3   | E 5 | 3     | 2    | l   |      |   | ı  | +   |     | E   | 1 6  | 2            | F   | 1 5 | 2    | F   | 4            | 2   | FC  | 1   | 3  | FS | 4   | 3 |    |      | ŀ   |    | ŀ   | ı   |     | - 1   | - 1  | -  | 4   | ı     | (3  | ) - |     |    | ۷   |

| SEC    | 1 → C                          |      |      |      |            | 1      |     | ı   |       |      |     |      |   |    | 3 2 |     | L   |      |              | ı   | 1   | 1    | 1   |              | İ   |     |     |    | l  |     |   |    |      |     |    | ł   | 1   | П   | -     |      | 1  | -   | -     | 1   | *   |     | -  | -   |

| SED    | 1 → D                          | L    | L    |      | _          | L      | L.  | L   | L     |      | L   | L    | Ļ |    |     | 1   |     | 1    | L            | L   | ↓   | L    | _   | Ļ            | L   | 1_  | L   | L  | L  | L   | 1 |    | 1    | L.  | L  | 1   | 1   | ⊥   | 4     | _    | _  | _   | _     | _   |     | _   | 1  | -   |

| SEI    | 1 - 1                          |      | I    |      |            | l      |     | l   |       |      | 1   |      | ĺ | 71 | 3 2 | 1   |     |      |              | ı   | İ   | l    | 1   |              | Ł   |     |     |    |    |     |   |    |      |     |    | f   | ı   | 1   | ı     |      | 1  | -   | -     | -   | 1   |     |    | -   |

| STA    | A - M                          |      | 1    |      |            |        |     | 85  |       |      | 1   |      |   | ı  | +   |     | 8   | 1 6  | 2            | 91  | 6   | 2    | 95  | 4            | 2   | 90  | 15  | 3  | 99 | 5   | 3 | 1  | 1    |     | L  |     | ĺ   | 1   |       |      |    | -   | -     | -   |     |     |    |     |

| STX    | x - M                          |      |      | 1    |            |        |     | 86  |       |      |     |      |   | į. |     |     | l   |      | 1            | ı   |     | 1    | 1   |              |     | 1   | ı   |    | l  | 1   | 1 |    |      |     |    |     | 1   | 9   | 96    | 4    | 2  | -   | -     | -   | -   |     | -  | -   |

| STY    | Y - M                          | i    |      |      | 8C         | 4      | 3   | 84  | 3     | 2    |     |      |   |    |     |     | 1   | 1    |              | ı   |     | 1    | 94  | 4            | 2   | 1   |     |    | l  |     | 1 | 1  |      |     | L  |     | İ   |     |       | į    |    | -   | -     | -   |     |     | -  |     |

| TAX    | <del></del>                    | ┖    | 1    | Ļ    | L          | 1      | ļ., | _   | 1     | L    | Ļ   | Ļ    | 1 |    | A 2 |     | _   | +    | ╀            | ₽   | +   | ┖    | L   | $\downarrow$ | Ļ   | ₽   | 1   | ļ_ | ļ  | 1   | ╀ | 1  | 1    | ļ., | L  | 4   | 1   | 4   | 4     | 4    | 4  |     | 1     | _=  |     | _   | -  | 4   |

| TAY    |                                | ı    | 1    |      |            |        |     |     |       |      |     | l    |   |    |     | 1   |     | i    |              | ı   |     | į.   |     |              |     | ļ   |     |    | l  | İ   | - | l  |      | ŀ   | ı  | ı   | 1   | 1   | -     | -    | -1 | ,   | J     | -   | -   |     | -  | -   |

| TSX    |                                | ı    | ļ    | 1    |            | Ĺ      | 1   | 1   |       | ı    |     |      |   | 1  | 4 2 |     | 1   |      |              | ı   |     | İ    |     |              | ŀ   | 1   | Ĺ   |    | l  | 1   |   | 1  |      |     | L  | ı   | ı   | 1   |       | 1    | ļ  | . 1 | ¥     | -   | -   | •   | -  | -   |

| TXA    | X - A                          | ı    |      |      |            | ļ      |     |     |       |      | 1   | i    |   |    | 2 م |     | ı   |      | ŀ            | ı   |     | i    |     | 1            |     | 1   |     |    | l  |     | 1 | ı  | ı    |     | L  |     | ı   |     |       | - 1  | ı  | . 1 | ٠     | -   | -   |     | -  | -   |

| TXS    | x - s                          | ı    | L    | ١.   |            | l      |     | ı   | 1     |      |     |      |   |    | 4 2 |     | l   |      |              | ı   |     | į    |     |              |     | 1   |     |    | l  |     |   | i  | 1    |     | L  | ı   | 1   | 1   |       | - 1  | ł  | -   | -     | -   | •   | •   | -  | -   |

| TYA    | Y - A                          | L_   | L    | L    | L          | L      | 上   | L   | L     | L    | L   | L.   | 1 | 9  | 8 2 | 1   | L.  | 1.   | I.           | L   | 1.  | L    | L   | L            | L   | L   | L   | L  | L  | L   | L | L  | 1    |     | L  | L   | L   | L   | ┙     | ┙    | _1 | 7   |       |     |     |     |    | 4   |

| (1)    | ADD 1 TO "N" IF PAGE BO        | UNI  | DAI  | ЯY   | IS (       | CR     | oss | ED  |       |      |     |      |   |    | ×   | ıs  | ΙĐΕ | ×    | ×            |     |     |      |     |              |     |     |     |    |    |     | ٠ | ΑĐ | Đ    |     |    |     |     |     |       |      | NO | 7 1 | ио    | DIE | :18 | D   |    | ŀ   |

| (2)    | ADD 1 TO "N" IF BRANCH         | 1 00 | ccu  | JRS  | т          | s.     | AM  | E P | AG    | E    |     |      |   |    | ٧   | IN  | ΙĐΕ | ×    | Y            |     |     |      |     |              |     |     |     |    |    |     |   | SU | BTF  | AC  | Ť  |     |     |     | N     | ۸, ۱ | ME | MC  | R.    | / B | μт  | 7   |    |     |

| 1 '    | ADD 2 TO "N" IF BRANCH         | 1 00 | CCL  | JA S | T(         | 0      | IF  | ER  | EN    | TF   | AG  | E    |   |    | A   | A   | ccu | JMI  | JLA          | то  | R   |      |     |              |     |     |     |    |    |     | ٨ | AN | 0    |     |    |     |     |     |       | , i  |    |     |       |     |     |     |    |     |

| (3) (  | CARRY NOT - BELOW              |      |      |      |            |        |     |     |       |      |     |      |   |    | M   | м   | ЕМ  | OFI  | Y P          | ER  | EF  | FE   | сті | ٧E           | A   | DOF | RES | s  | _  |     | v | OR |      |     |    |     |     |     | ١     | v i  | NO | , ( | YC    | :16 | s   |     |    | -   |

|        | F IN DECIMAL MODE Z F          |      |      |      |            |        |     |     |       |      |     |      |   |    |     |     |     |      |              |     | ST  |      |     |              |     |     |     |    |    |     |   |    | CLL  | JSI | VE | OF  | ŧ   |     |       |      | NO |     | ΥT    | €S  |     |     |    | - 1 |

| 1 ,    | ACCUMULATOR MUST BE            | CH   | EC   | KE   | ) F        | OR     | Ζŧ  | RO  | R     | ESι  | JLT |      |   |    |     |     |     |      |              |     | 6   |      |     |              |     |     |     |    |    |     | , | MC | OH   | 16  | D. |     |     |     |       |      |    |     |       |     |     |     |    | - 1 |

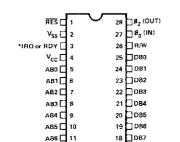

### SY6503 - 28 Pin Package

AB10 [

AB11 20

15 AB9

17 A812 16 AB11

15 AB10

22 AB12 ט ע<sub>ss</sub>

21

### **Features**

- 4K Addressable Bytes of Memory (AB00-AB11)

- · On-the-chip Clock

- IRQ Interrupt

- NMI Interrupt

- 8 Bit Bi-Directional Data Bus

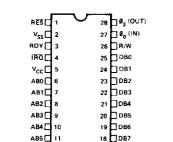

### SY6504 & SY6507 - 28 Pin Package

ABB 🔲 14

AB7 🗖 12

АВВ 🗀 13 AB9 🔲

### **Features**

- IRQ Interrupt (6504 only)

- RDY Signal (6507 only)

- 8K Addressable Bytes of Memory (AB00-AB12)

- On-the-chip Clock

- 8 Bit Bi-Directional Data Bus

### SY6505 — 28 Pin Package

17 AB11 16 AB10

15 AB9

### Features

- 4K Addressable Bytes of Memory (AB00-AB11)

- On-the-chip Clock

- IRQ Interrupt

- RDY Signal

- 8 Bit Bi-Directional Data Bus

### SY6506 — 28 Pin Package

AB6 12

AB7 ☐ 13 AB8 ☐ 14

### Features

- 4K Addressable Bytes of Memory (AB00-AB11)

On-the-chip Clock

- IRQ Interrupt

- Two phases off

- 8 Bit Bi-Directional Data Bus

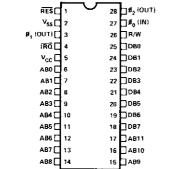

### SY6512 - 40 Pin Package

AB4 [ 13

AB6 | 15 AB7 | 16

AB8 77

AB9 18

AB10 🔲 19

A85 🗌

| 1                 |    |    |                         |

|-------------------|----|----|-------------------------|

| ∨ <sub>ss</sub> ⊏ | 1  | 40 | TRES                    |

| RDY 🗆             | 2  | 39 | ``]ø <sub>2</sub> (Ουτ) |

| #, □              | 3  | 38 | ] s.o.                  |

| IRG.□             | 4  | 37 | <b>□</b> 0₂             |

| Vss □             | 5  | 36 | DBE                     |

| NIMI)             | 6  | 35 | ⊒N,C.                   |

| SYNC              | 7  | 34 | □R/W                    |

| v <sub>cc</sub> □ | θ  | 33 | □D80                    |

| AB0 [             | 9  | 32 | _D81                    |

| AB1 ☐             | 10 | 31 | □0B2                    |

| AB2 [             | 11 | 30 | DB3                     |

| AB3 [             | 12 | 29 | DB4                     |

28 DB5

26 DB7

25 AB16

24 AB14

23 AB13

22 AB12

21 V<sub>SS</sub>

## Features

- 65K Addressable Bytes of Memory

- IRQ Interrupt

NMI Interrupt

RDY Signal

- 8 Bit Bi-Directional Data Bus

- SYNC Signal

- Two phase input

- Data Bus Enable

### SY6513 - 28 Pin Package

16 AB10

15 A89

### **Features**

- 4K Addressable Bytes of Memory (AB00-AB11)

- Two phase clock input

- IRQ Interrupt

- NMI Interrupt

- 8 Bit Bi-Directional Data Bus

### SY6514 - 28 Pin Package

AB7 🔲 13

AB8 14

### **Features**

- 8K Addressable Bytes of Memory (AB00-AB12)

- . Two phase clock input

- IRQ Interrupt

- 8 Bit Bi-Directional Data Bus

### SY6515 - 28 Pin Package

AB9 14

AB8 🔲 14

15 AB9

### **Features**

- 4K Addressable Bytes of Memory (AB00-AB11)

- Two phase clock input

- IRQ Interrupt

- 8 Bit Bi-Directional Data Bus

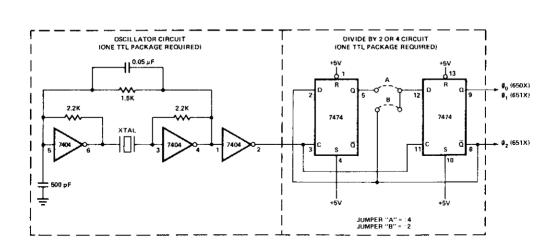

### **CLOCK GENERATION CIRCUITS**

| CRYSTAL      | OUTPUT F     | REQUENCY     |

|--------------|--------------|--------------|

| FREQUENCY    | · 2          | -4           |

| 3.579545 MHz | 1.7897 MHz   | 0.894886 MHz |

| 4.194304 MHz | 2.097152 MHz | 1.048576 MHz |

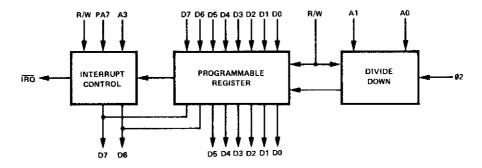

# APPENDIX J SY6522 DATA SHEET

### SY6522 SY6522A

### MICROPROCESSOR **PRODUCTS**

Preliminary

**APRIL 1979**

- Two 8-Rit Ridirectional I/O Ports

- Two 16-Bit Programmable Timer/Counters

- Serial Data Port

- Single +5V Power Supply

- TTL Compatible

- CMOS Compatible Peripheral Control Lines

- Expanded "Handshake" Canability Allows Positive Control of Data Transfers Between Processor and Peripheral Devices

- Latched Output and Input Begisters

- 1 MHz and 2 MHz Operation

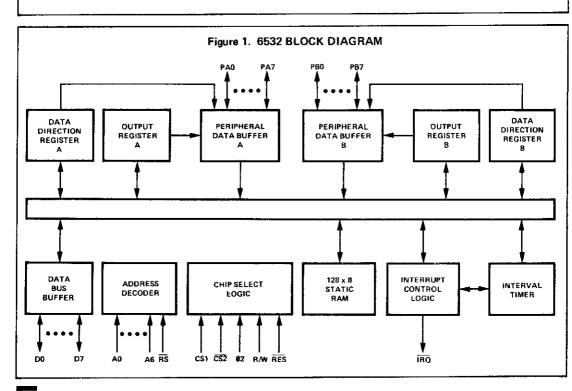

The SY6522 Versatile Interface Adapter (VIA) is a very flexible I/O control device. In addition, this device contains a pair of very powerful 16-bit interval timers, a serial-to-parallel/parallel-to-serial shift register and input data latching on the peripheral ports. Expanded handshaking capability allows control of bi-directional data transfers between VIA's in multiple processor systems.

Control of peripheral devices is handled primarily through two 8-bit bi-directional ports. Each line can be programmed as either an input or an output. Several peripheral I/O lines can be controlled directly from the interval timers for generating programmable frequency square waves or for counting externally generated pulses. To facilitate control of the many powerful features of this chip, an interrupt flag register, an interrupt enable register and a pair of function control registers are provided.

### **ABSOLUTE MAXIMUM RATINGS**

| Rating                       | Symbol           | Value                        | Unit |

|------------------------------|------------------|------------------------------|------|

| Supply Voltage               | Vcc              | -0.3 to +7.0                 | ٧    |

| Input Voltage                | VIN              | -0.3 to +7.0<br>-0.3 to +7.0 | V    |

| Operating Temperature        | 1                | 0 to +70                     | °c.  |

| Range<br>Storage Temperature | T <sub>A</sub>   | 0 10 +70                     | `    |

| Range                        | T <sub>stg</sub> | -55 to +150                  | °C   |

This device contains circuitry to protect the inputs against damage due to high static voltages. However, it is advised that normal precautions be taken to avoid application of any voltage higher than maximum rated voltages.

### ELECTRICAL CHARACTERISTICS (V<sub>CC</sub> = 5.0V ± 5%, T<sub>A</sub> = 0-70°C unless otherwise noted)

| Symbol           | Characteristic                                                                                                                         | Min.         | Max.     | Unit     |

|------------------|----------------------------------------------------------------------------------------------------------------------------------------|--------------|----------|----------|

| V <sub>IH</sub>  | Input High Voltage (all except $\phi$ 2)                                                                                               | 2.4          | Vcc      | V        |

| V <sub>CH</sub>  | Clock High Voltage                                                                                                                     | 2.4          | Vcc      | V        |

| VIL              | Input Low Voltage                                                                                                                      | -0.3         | 0.4      | V        |

| I <sub>IN</sub>  | Input Leakage Current $-$ V <sub>IN</sub> = 0 to 5 Vdc R/W, RES, RS0, RS1, RS2, RS3, CS1, $\overline{CS2}$ , CA1, $\Phi$ 2             | -            | ±2.5     | μА       |

| <sup>†</sup> TSI | Off-state Input Current - V <sub>IN</sub> = .4 to 2.4V<br>V <sub>CC</sub> = Max, D0 to D7                                              | _            | ±10      | μΑ       |

| I <sub>IH</sub>  | Input High Current — V <sub>IH</sub> = 2.4V<br>PA0-PA7, CA2, PB0-PB7, CB1, CB2                                                         | -100         | _        | μΑ       |

| I <sub>IL</sub>  | Input Low Current — V <sub>IL</sub> = 0.4 Vdc<br>PA0-PA7, CA2, PB0-PB7, CB1, CB2                                                       | _            | -1.6     | mA       |

| V <sub>OH</sub>  | Output High Voltage<br>V <sub>CC</sub> = min, I <sub>load</sub> = -100 μAdc<br>PA0-PA7, CA2, PB0-PB7, CB1, CB2                         | 2.4          | _        | V        |

| VoL              | Output Low Voltage<br>V <sub>CC</sub> = min, I <sub>load</sub> = 1.6 mAdc                                                              | -            | 0.4      | V        |

| Юн               | Output High Current (Sourcing)  VOH = 2.4V  VOH = 1.5V (PB0-PB7)                                                                       | -100<br>-1.0 | _<br>    | μA mA    |

| loL              | Output Low Current (Sinking) VOL = 0.4 Vdc                                                                                             | 1.6          | -        | mA       |

| OFF              | Output Leakage Current (Off state)                                                                                                     | -            | 10       | μА       |

| C <sub>IN</sub>  | Input Capacitance — T <sub>A</sub> = 25°C, f = 1 MHz<br>(R/W, RES, RS0, RS1, RS2, RS3, CS1, CS2,<br>D0-D7, PA0-PA7, CA1, CA2, PB0-PB7) | _            | 7.0      | pF       |

|                  | (CB1, CB2)<br>(Φ2 Input)                                                                                                               |              | 10<br>20 | pF<br>pF |

| C <sub>OUT</sub> | Output Capacitance — T <sub>A</sub> = 25°C, f = 1 MHz                                                                                  |              | 10       | pF       |

| PD               | Power Dissipation                                                                                                                      |              | 700      | mW       |

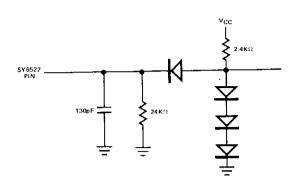

Figure 2. Test Load (for all Dynamic Parameters)

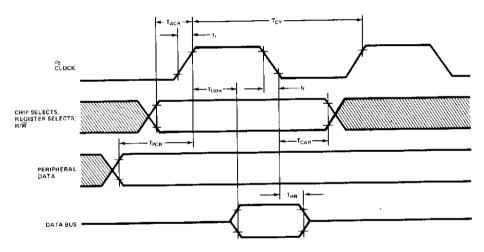

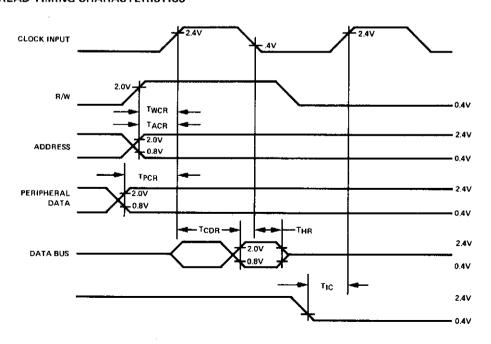

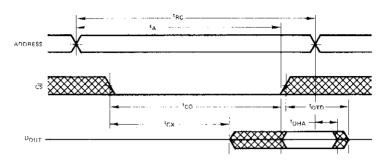

Figure 3. Read Timing Characteristics

### **READ TIMING CHARACTERISTICS (FIGURE 3)**

|                  |                             | SY   | 6522 | SY6  | 522A |      |

|------------------|-----------------------------|------|------|------|------|------|

| Symbol           | Parameter                   | Min. | Max. | Min. | Max. | Unit |

| T <sub>CY</sub>  | Cycle Time                  | 1    | 50   | 0.5  | 50   | μs   |

| T <sub>ACR</sub> | Address Set-Up Time         | 180  |      | 90   | -    | ns   |

| TCAR             | Address Hold Time           | 0    |      | 0    | _    | ns   |

| T <sub>PCB</sub> | Peripheral Data Set-Up Time | 300  | _    | 300  |      | ns   |

| TCDR             | Data Bus Delay Time         | _    | 395  | _    | 200  | ns   |

| THR              | Data Bus Hold Time          | 10   | -    | 10   |      | ns   |

NOTE: tr, tf = 10 to 30ns.

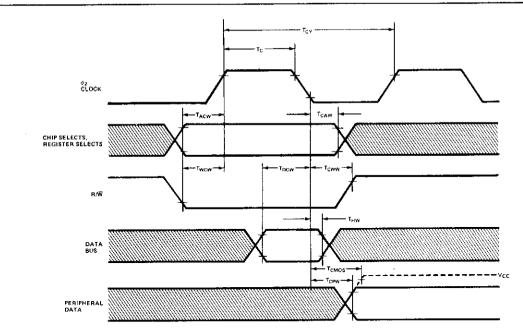

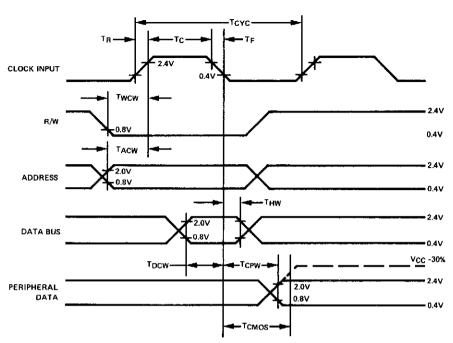

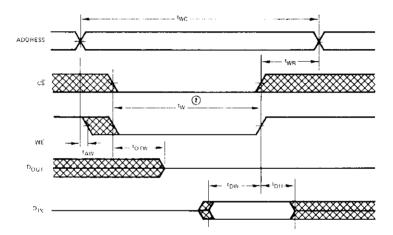

Figure 4. Write Timing Characteristics

### WRITE TIMING CHARACTERISTICS (FIGURE 4)

|                   | <del></del> . <del>~</del>                   | SY6  | 522  | SY65 | 1    |      |

|-------------------|----------------------------------------------|------|------|------|------|------|

| Symbol            | Parameter                                    | Min. | Max. | Min. | Max. | Unit |

| T <sub>CY</sub>   | Cycle Time                                   | 1    | 50   | 0.50 | 50   | μς   |

| T <sub>C</sub>    | φ2 Pulse Width                               | 0.47 | 25   | 0.25 | 25   | μs   |

| TACW              | Address Set-Up Time                          | 180  |      | 90   | _    | ns   |

| T <sub>CAW</sub>  | Address Hold Time                            | 0    | -    | 0    |      | ns   |

| T <sub>WCW</sub>  | R/W Set-Up Time                              | 180  | _    | 90   | _    | ns   |

| Tcww              | R/W Hold Time                                | 0    | -    | 0    | _    | ns   |

| T <sub>DCW</sub>  | Data Bus Set-Up Time                         | 300  |      | 150  | -    | ns   |

| T <sub>HW</sub>   | Data Bus Hold Time                           | 10   | _    | 10   | -    | ns   |

| T <sub>CPW</sub>  | Peripheral Data Delay Time                   | _    | 1.0  | _    | 1.0  | μς   |

| T <sub>CMOS</sub> | Peripheral Data Delay Time<br>to CMOS Levels | _    | 2.0  | -    | 2.0  | μs   |

NOTE: tr, tf = 10 to 30ns.

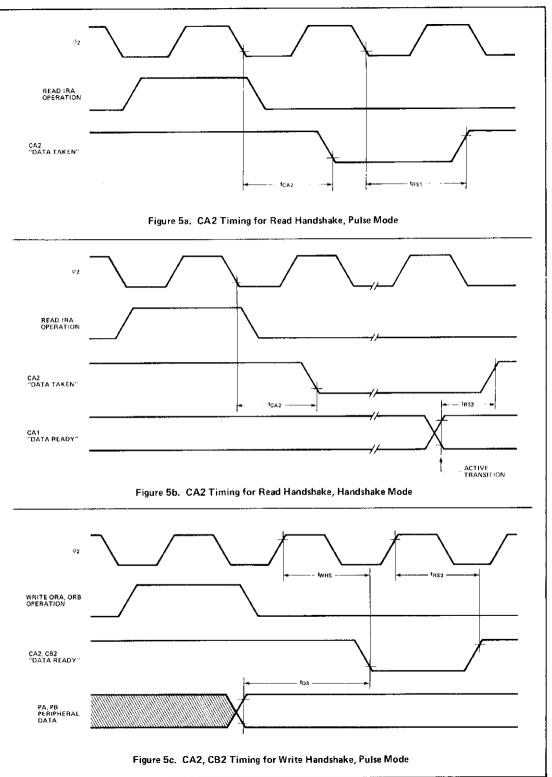

### PERIPHERAL INTERFACE CHARACTERISTICS

| Symbol                          | Characteristic                                                                                     | Min. | Max. | Unit | Figure         |

|---------------------------------|----------------------------------------------------------------------------------------------------|------|------|------|----------------|

| t <sub>r</sub> , t <sub>f</sub> | Rise and Fall Time for CA1, CB1, CA2, and CB2<br>Input Signals                                     | _    | 1.0  | μs   | _              |

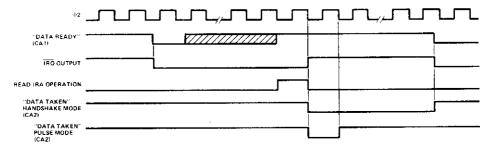

| T <sub>CA2</sub>                | Delay Time, Clock Negative Transition to CA2 Negative<br>Transition (read handshake or pulse mode) | -    | 1.0  | μs   | 5a, <b>5</b> b |

| T <sub>RS1</sub>                | Delay Time, Clock Negative Transition to CA2 Positive<br>Transition (pulse mode)                   | _    | 1.0  | μs   | 5a             |

| T <sub>RS2</sub>                | Delay Time, CA1 Active Transition to CA2 Positive<br>Transition (handshake mode)                   |      | 2.0  | μς   | <b>5</b> b     |

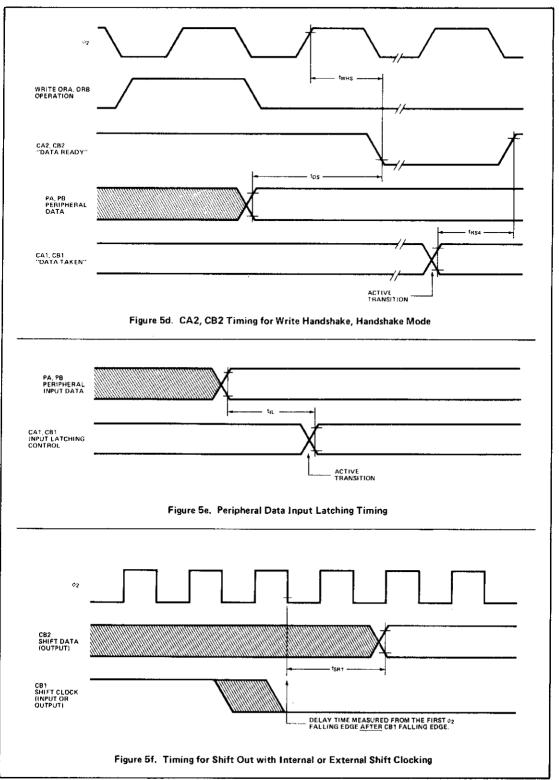

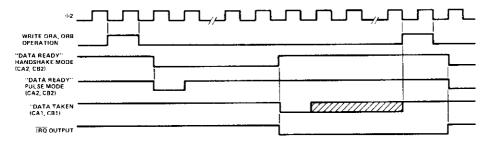

| T <sub>WHS</sub>                | Delay Time, Clock Positive Transition to CA2 or CB2<br>Negative Transition (write handshake)       | -    | 1.0  | μs   | 5c, 5d         |

| Tos                             | Delay Time, Peripheral Data Valid to CB2 Negative<br>Transition                                    |      | 1,5  | μs   | 5c, 5d         |

| T <sub>RS3</sub>                | Delay Time, Clock Positive Transition to CA2 or CB2<br>Positive Transition (pulse mode)            | _    | 1.0  | μs   | 5c             |

| T <sub>RS4</sub>                | Delay Time, CA1 or CB1 Active Transition to CA2 or CB2 Positive Transition (handshake mode)        |      | 2.0  | μs   | 5d             |

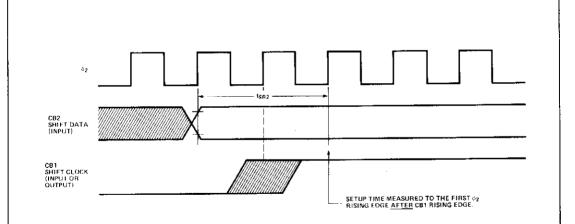

| TIL                             | Set-up Time, Peripheral Data Valid to CA1 or CB1<br>Active Transition (input latching)             | 300  | _    | ns   | 5e             |

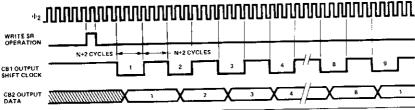

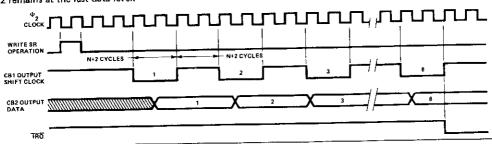

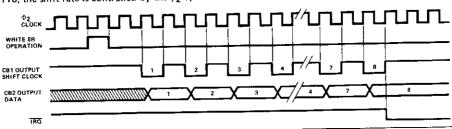

| T <sub>SR1</sub>                | Shift-Out Delay Time — Time from $\phi_2$ Falling Edge to CB2 Data Out                             | -    | 300  | ns   | 5f             |

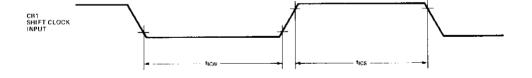

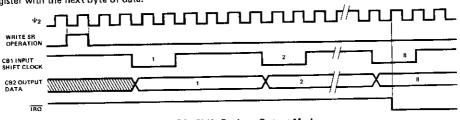

| T <sub>SR2</sub>                | Shift-In Setup Time – Time from CB2 Data In to $\phi_2$ Rising Edge                                | 300  | -    | ns   | <b>5</b> g     |

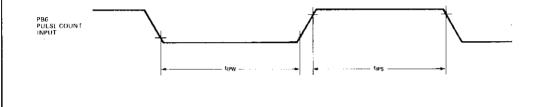

| T <sub>IPW</sub>                | Pulse Width — PB6 Input Pulse                                                                      | 2    | _    | μs   | 5í             |

| Ticw                            | Pulse Width — CB1 Input Clock                                                                      | 2    | _    | μs   | 5h             |

| I <sub>IPS</sub>                | Pulse Spacing — PB6 Input Pulse                                                                    | 2    | -    | μs   | 5i             |

| lics                            | Pulse Spacing — CB1 Input Pulse                                                                    | 2    |      | μs   | 5h             |

Figure 5g. Timing for Shift In with Internal or External Shift Clocking

Figure 5h, External Shift Clock Timing

Figure 5i. Pulse Count Input Timing

### PIN DESCRIPTIONS

### RES (Reset)

The reset input clears all internal registers to logic 0 (except T1 and T2 latches and counters and the Shift Register). This places all peripheral interface lines in the input state, disables the timers, shift register, etc. and disables interrupting from the chip.

### φ2 (Input Clock)

The input clock is the system  $\phi 2$  clock and is used to trigger all data transfers between the system processor and the SY6522.

### R/W (Read/Write)

The direction of the data transfers between the SY6522 and the system processor is controlled by the  $R/\overline{W}$  line. If R/W is low, data will be transferred out of the processor into the selected SY6522 register (write operation). If R/W is high and the chip is selected, data will be transferred out of the SY6522 (read operation).

### DB0-DB7 (Data Bus)

The eight bi-directional data bus lines are used to transfer data between the SY6522 and the system processor. During read cycles, the contents of the selected SY6522 register are placed on the data bus lines and transferred into the processor. During write cycles, these lines are high-impedance inputs and data is transferred from the processor into the selected register. When the SY6522 is unselected, the data bus lines are high-impedance.

### CS1, CS2 (Chip Selects)

The two chip select inputs are normally connected to processor address lines either directly or through decoding. The selected SY6522 register will be accessed when CS1 is high and  $\overline{\text{CS2}}$  is low.

### RS0-RS3 (Register Selects)

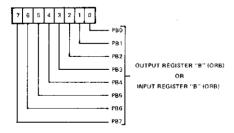

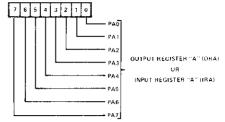

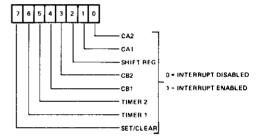

The four Register Select inputs permit the system processor to select one of the 16 internal registers of the SY6522, as shown in Figure 6.

| Register RS Coding |         | Register | Description |   |         |                                     |                      |  |  |

|--------------------|---------|----------|-------------|---|---------|-------------------------------------|----------------------|--|--|

| Number             | RS3 RS2 |          | RS1 RS0     |   | Desig.  | Write                               | Read                 |  |  |

| 0                  | 0       | 0        | 0           | 0 | ORB/IRB | Output Register "B"                 | Input Register "B"   |  |  |

| 1                  | 0       | 0        | 0           | 1 | ORA/IRA | Output Register "A"                 | Input Register "A"   |  |  |

| 2                  | 0       | 0        | 1           | 0 | DDRB    | Data Direction Register "B"         |                      |  |  |

| 3                  | 0       | 0        | 1           | 1 | DDRA    | Data Direction Register             | 'A''                 |  |  |

| 4                  | 0       | 1        | 0           | 0 | T1C-L   | T1 Low-Order Latches                | T1 Low-Order Counter |  |  |

| 5                  | 0       | 1        | 0           | 1 | T1C-H   | T1 High-Order Counter               |                      |  |  |

| 6                  | 0       | 1        | 1           | 0 | T1L-L   | T1 Low-Order Latches                |                      |  |  |

| 7                  | 0       | 1        | 1           | 1 | T1L-H   | T1 High-Order Latches               |                      |  |  |

| 8                  | 1       | 0        | 0           | 0 | T2C-L   | T2 Low-Order Latches                | T2 Low-Order Counter |  |  |

| 9                  | 1       | 0        | 0           | 1 | T2C-H   | T2 High-Order Counter               |                      |  |  |

| 10                 | 1       | 0        | 1           | 0 | SR      | Shift Register                      |                      |  |  |

| 11                 | 1       | 0        | 1           | 1 | ACR     | Auxiliary Control Register          |                      |  |  |

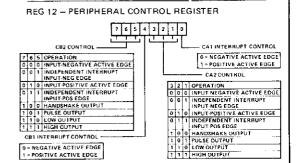

| 12                 | 1       | 1        | 0           | 0 | PCR     | Peripheral Control Register         |                      |  |  |

| 13                 | 1       | 1        | 0           | 1 | IFR     | Interrupt Flag Register             |                      |  |  |

| 14                 | 1       | 1        | 1           | 0 | IER     | Interrupt Enable Register           |                      |  |  |

| 15                 | 1 1     | 1        | 1           | 1 | ORA/IRA | Same as Reg 1 Except No "Handshake" |                      |  |  |

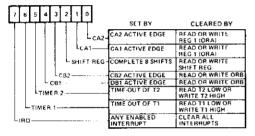

Figure 6. SY6522 Internal Register Summary

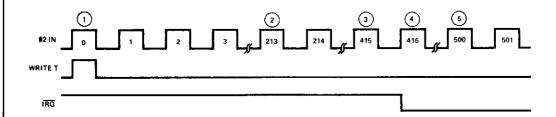

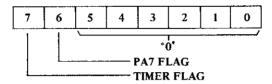

### IRQ (Interrupt Request)

The Interrupt Request output goes low whenever an internal interrupt flag is set and the corresponding interrupt enable bit is a logic 1. This output is "opendrain" to allow the interrupt request signal to be "wire-or'ed" with other equivalent signals in the system.

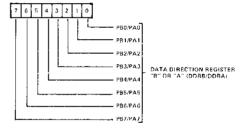

### PAO-PA7 (Peripheral A Port)

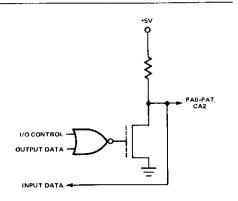

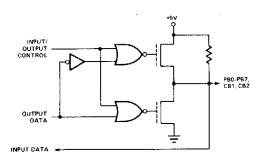

The Peripheral A port consists of 8 lines which can be individually programmed to act as inputs or outputs under control of a Data Direction Register. The polarity of output pins is controlled by an Output Register and input data may be latched into an internal register under control of the CA1 line. All of these modes of operation are controlled by the system processor through the internal control registers. These lines represent one standard TTL load in the input mode and will drive one standard TTL load in the output mode. Figure 7 illustrates the output circuit.

### CA1, CA2 (Peripheral A Control Lines)