# Popular Electronics®

WORLD'S LARGEST-SELLING ELECTRONICS MAGAZINE

**DECEMBER 1980/95¢**

Build a Digital Phono Stylus Timer

Comparing Electronic Games

Low-Cost Computer-Memory Expansion

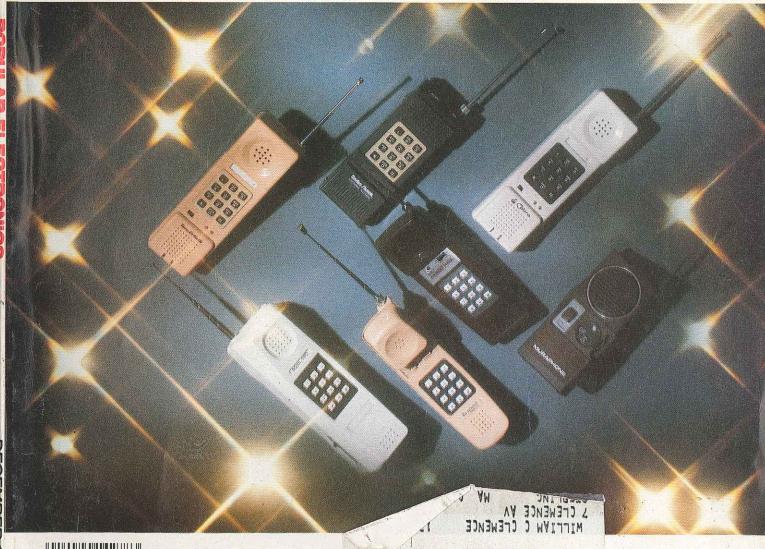

New Cordless Telephones for the Home

SPECIAL SI

POPPER CEM ODOSCODE IFID NOVEZ

The Electronic World

Start learning and computing for only \$129.95 with a Netronics 8085-based computer kit. Then expand it in low-cost steps to a business/development system with 64k or more RAM, 8" floppy disk drives, hard disks and multi-terminal I/O.

## THE NEW EXPLORER/85 SYSTEM

Special! Full 8" floppy, 64k system for less than the price of a mini! Only \$1499.95!

Imagine — for only \$129.95 you can own the starting level of Explorer/85, a computer that's expandable into full business/development capabilities — a computer that can be your beginner system, an OEM controller, or an IBM-formatted 8" disk small business system. From the first day you own Explorer/85, you begin computing on a significant level, and applying principles discussed in leading computer magazines. Explorer/85 features the advanced Intel 8085 cpu, which is 100% compatible with the older 8080A. It offers onboard S-100 bus expansion, Microsoft BASIC in ROM, plus instant conversion to mass storage disk memory with standard IBM-formatted 8" disks. All for only \$129.95, plus the cost of power supply, keyboard/ terminal and RF modulator if you don't have them (see our remarkable prices below for these and other ac-cessories). With a Hex Keypad/display front panel, Level "A" can be programmed with no need for a ter-minal, ideal for a controller, OEM, or a real low-cost

Level "A" is a system, perfect for eginners, hobbyists, ndustrial controlle use. \$129.95

LEVEL "A" SPECIFICATIONS

Explorer/85's Level "A" system features the advanced Intel 8085 cpu, an 8355 ROM with 2k deluxe monitor/ operating system, and an advanced 8155 RAM I/O . . . all on a single motherboard with room for RAM/ROM/PROM/FREMOM and \$100 expension. PROM/EPROM and S-100 expansion, plus generous

prototyping space.

PC Board: Glass epoxy, plated through holes with solder mask. • I/O: Provisions for 25-pin (DB25) connector for terminal serial I/O, which can also support a paper tape reader . . . cassette tape recorder input and paper tape reader ... cassette tape recorder input and output ... cassette tape control output ... LED output indicator on SOD (serial output) line ... printer interface (less drivers) ... total of four 8-bit plus one 6-bit I/O ports . Crystal Frequency: 6.144 MHz. · Control Switches: Reset and user (RST 7.5) interrupt ... additional provisions for RST 5.5, 6.5 and TRAP interrupts onboard. • Counter/Timer: Programmable, 14-bit bi nary. · System RAM: 256 bytes located at F800, ideal nary. • System RAM: 256 bytes located at Foot, iteal for smaller systems and for use as an isolated stack area in expanded systems . . . RAM expandable to 64K via S-100 bus or 4k on motherboard.

System Monitor (Terminal Version): 2k bytes of deluxe system monitor ROM located at FMM, leaving MMM free for user RAM/ROM. Features include tape

19800 free for user RAM/ROM. reatures include tape load with labeling ... examine/change contents of memory ... insert data ... warm start ... examine and change all registers ... single step with register display at each break point, a debugging/training feature ... go to execution address ... move blocks of memory from one location to another ... fill blocks of memory with a constant ... display blocks of memory ... automatic baud rate selection to 9600 baud ... variable display line length coated [1.255 characters/line] ... chanline length control (1-255 characters/line) ... chan-nelized I/O monitor routine with 8-bit parallel output for high-speed printer . . . serial console in and console out channel so that monitor can communicate with I/O

System Monitor (Hex Keypad/Display Version): Tape load with labeling ... tape dump with labeling ... examine/change contents of memory ... insert data ... warm start ... examine and change all registers ...

Full 8" disk system for less than the price of a mini (shown with Netronics Explorer/85 computer and new terminal). System features floppy drive from Control Data Corp., world's largest maker of ory storage systems (<u>not</u> a hobby brand!)

single step with register display at each break point . . . . go to execution address. Level "A" in this version makes a perfect controller for industrial applications. and is programmed using the Netronics Hex Keypad/ Display. It is low cost, perfect for beginners.

HEX KEYPAD/DISPLAY SPECIFICATIONS Calculator type keypad with 24 system-defined and 16 user-defined keys. Six digit calculator-type display, that displays full address plus data as well as register nd status information

LEVEL "B" SPECIFICATIONS

LEVEL "B" SPECIFICATIONS

Level "B" provides the S-100 signals plus buffers/

drivers to support up to six S-100 bus boards, and includes: address decoding for onboard 4k RAM expansion selectable in 4k blocks ... address decoding for

onboard 8k EPROM expansion selectable in 8k blocks , address and data bus drivers for onboard expansion wait state generator (jumper selectable), to allow the use of slower memories . . . two separate 5 volt regula-

LEVEL "C" SPECIFICATIONS

Level "C" expands Explorer/85's motherboard with a card cage, allowing you to plug up to six S-100 cards directly into the motherboard. Both cage and card are neally contained inside Explorer's deluxe steel cabinet. Level "C" includes a sheet metal superstruc-ture, a 5-card, gold plated S-100 extension PC board that plugs into the motherboard. Just add required

LEVEL "D" SPECIFICATIONS

Level "D" provides 4k of RAM, power supply regula-tion, filtering decoupling components and sockets to expand your Explorer/85 memory to 4k (plus the origi-

Explorer/85

nal 256 bytes located in the 8155A). The static RAM can be located anywhere from 60000 to EFFF in 4k

LEVEL "E" SPECIFICATIONS

LEVEL "E" SPECIFICATIONS

Level "E" adds sockets for 8k of EPROM to use the

popular Intel 2716 or the TI 2516. It includes all sockets,

power supply regulator, heat sink, filtering and decoupling components. Sockets may also be used for 2k x 8

RAM IC's (allowing for up to 12k of onboard RAM). DISK DRIVE SPECIFICATIONS

- Data capacity: 401,016 bytes (SD), 802,032 bytes (DD). "CONTROL DATA CORP.

- unformatted.

Access time: 25ms (one

- DISK CONTROLLER/ I/O BOARD SPECIFICATIONS

- 2716 PROM socket included Controls up to four 8" drive 1771A LSI (SD) floppy disk

- for use in custom

applications.

Onboard crystal controlled.

Onboard I/O baud rate

generators to 9600 baud.

Double-sided PC board Onboard data separator 2 Serial I/O ports

Autoboot to disk system

- DISK DRIVE CABINET/POWER SUPPLY

**ORDER A COORDINATED**

### **EXPLORER/85 APPLICATIONS** PAK!

Beginner's Pak (Save \$26.00!) — Buy Level "A" (Terminal Version) with Monitor Source Listing and AP-1 5-amp Power Supply: (regular price \$199.95), now at SPECIAL PRICE: \$169.95 plus post. & insur. Experimenter's Pak II (Save \$53.40!) — Buy Level

Experimenter's Pak II (Save \$53.40f) — Buy Seve "A" (Hex Keypad/Display Version) with Hex Keypad/Display, Intel 8085 User Manual, Level "A" Hex Monitor Source Listing, and AP-15-amp Power Supply: (regular price \$279.35), all at SPECIAL PRICE: \$219.95 plus post. & insur.

PRICE: \$219.95 plus post. & insur.

Special Microsoft BASIC Pak (Save \$103.00!) — Includes Level "A" (Terminal Version), Level "B".

Level "D" (4k RAM), Level "E", 8k Microsoft in ROM, Intel 8085 User Manual, Level "A" Monitor Source Listing, and AP-15-amp Power Supply: (regular price \$439.70), now yours at SPECIAL PRICE: \$329.95 plus post. & insur.

ADD A TERMINAL WITH CABINET,

GET A FREE RF MODULATOR: Save over \$114 at this SPECIAL PRICE: \$499.95

plus post. & insur. Special 8" Disk Edition Explorer/85 (Save over \$104!) Includes disk-version Level "A", Level "B", two S-100 connectors and brackets, disk controller, 64k S-100 connectors and brackets, this controller, who RAM, AP-15-amp power supply, Explorer/85 deluxe steel cabinet, cabinet fan, 8" SD/DD disk drive from famous CONTROL DATA CORP. (not a hobby brandl), drive cabinet with power supply, and drive cable set-up for two drives. This package includes everything but terminal and printers (see coupon for them). Regular price \$1630.30, all yours in kit a SPECIAL PRICE: \$1499.95 plus post. & insur. Wired and tested, only \$1799.95.

Special! Complete Business Software Pak (Save \$625.00!) — Includes CP/M 2.0. Microsoft BASIC. General Ledger, Accounts Receivable, Accounts Payable, Payroll Package; (regular price \$1325), yours now at SPECIAL PRICE: \$699.95.

can perform reasonably well, but its small memory locks it out of using much sophisticated software. In most systems, memory can be expanded by installing memory chip sets or plug-in memory boards. However, in the particular case of the Radio Shack TRS-80, installation of a RAM chip set leaves 16K inside the machine and 4K of removed RAM unused. Actually, this can be a bonus if you build the memory board and expansion interface described in this article. The modification detailed here pro-

MICROCOMPUTER with 4K of RAM (random access memory)

vides a total of 20K of RAM and a plugboard system that allows experiments with I/O ports. The memory board features a universal address decoder that allows placing the RAM on any 4K boundary. If you program in machine language using the TRS-80 TBUG monitor, you can switch the memory block to the remote end of memory where the small utility program really belongs. Also, the board is easily converted to accept 16K RAMs if desired.

The simplicity of memory upgrade from 4K to 16K is the direct result of the use of 16-pin RAM chips. These multiplexed-address input dynamic RAMs are in wide application because of their low cost and power consumption. The latest additions to this family of devices provide up to 64K bytes with eight memory chips.

Memory Basics. The Z80 microprocessor distinguishes memory access machine cycles by concurrently issuing a 16-bit memory address and memory request (MREQ), along with either a read (RD) or write (WR) pulse. These and other control signals operate the memory blocks of a computer. A typical memory chip includes address input, write, chipselect (or chip-enable), and data input and output lines.

Computer memory consists of a number of memory blocks arranged in sequence. A memory block may consist of one 1K × 8 read-only memory (ROM), two 1K × 4 RAMs, or eight 16K × 1 RAMs, to name a few of the possible configurations. Whatever the chip size, the storage elements of the device are arranged in a matrix. For example, the storage matrix of the 4027 (4K × 1) chip consists of 64 rows by 64 columns, yielding 4096 bits. A memory element within the matrix is selected by matrix row and column decoders. For a 4K × 1 memory chip, the address decode range is from 000 (zero) to FFF hexadecimal or 4096 decimal.

To allow stacking memory blocks end-to-end, an external memory address decoder is required. The address decoder continuously scans the higher-order computer address lines and exclusively

PLUG-BOARD SYSTEM FOR ADDING 16K OF DYNAMIC RAM WITH A 4K BONUS BY ADOLPH A. MANGIERI

TRS-80 MEMORY

#### Please send the items checked below:

- ☐ Explorer/85 Level "A" kdt (Terminal Version)... \$129.95 plus

- "E"). \$99,95 plus \$2 post. & insur.

□ Level "B" (\$-100) klt... \$49,95 plus \$2 post. & insur.

□ Level "C" (\$-100 6-card expander) klt... \$39,95 plus \$2 post.

- & insur.

Level "D" (4k RAM) kit . . . \$69.95 plus \$2 post. & insur.

Level "B" (EPROW/ROM) kit . . . \$5.95 plus 50¢ p&h.

Deluxe Steel Cabinet for Explorer/85 . . . \$49.95 plus \$3 post.

- & insur.

☐ Fan For Cabinet . . . \$15.00 plus \$1.50 post. & insur.

☐ ASCII Keyboard/Computer Terminal kit: features a full 128 character set. u&l case; full cursor control: 75 ohm video output; convertible to baudot output; selectable baud rate. RS232-C or 20 ma. I/O. 32 or 64 character by 16 line formats. RS232-C or 20 ma. 170. 32 of or database 137 soft of the and can be used with either a CRT monitor or a TV set (if you have an RF modulator)... \$149.95 plus \$3.00 post, & insur.

DeLuxe Steel Cabinet for ASCII keyboard/terminal...

- □ DeLuxe Steet cannet for ASCLT keyboardurerman ...

S19.95 plus \$2.50 post. & insur.

□ New! Terminal Monitor: (See photo) Same features as above. except 12" monitor with keyboard and terminal is in deluxe single cabinet: kit... \$399.95 plus \$7 post. & insur.

□ Hazeltine terminals: Our prices too low to quote CALL US

□ Lear-Sigler terminals/printers: Our prices too low to quote:

- ☐ Hex Keypad/Display kit . . . \$69.95 plus \$2 post. & insur.

- ☐ AP-1 Power Supply Kit ±8V @ 5 amps) in deluxe steel cabinet ... \$39.95 plus \$2 post. & insur.

Gold Plated S-100 Bus Connectors ... \$4.85 each, postpaid.

RF Modulator kit (allows you to use your TV set as a monitor)

- ...\$8.95 postpaid.

I 16k RAM kit (5-100 board expands to 64k)...\$199.95 plus \$2

- 7 32k RAM kit... \$299,95 plus \$2 post. & insur.

- □ 32K KAM KII... \$2498.49 DIUS \$2 post. & Insur. □ 48k RAM kit... \$399.95 plus \$2 post. & insur. □ 64k RAM Expansion kit (to expand any of the above in 16k blocks up to 64k)... \$99.95 plus \$2 post. & insur. each. □ Intel 8095 cpu Users' Manual... \$7.50 postpaid. □ 12' Video Monitor (10MHz bandwidth)... \$139.95 plus \$5 post. & insur.

- post, & insur. Beginner's Pak (see above) \$169.95 plus \$4 post, & insur. Experimenter's Pak (see above) . . . \$219.95 plus \$6 post, &

- insur.

Special Microsoft BASIC Pak Without Terminal (see above)...

\$329.95 plus \$7 post. & insur.

Same as above, plus ASCII Keyboard Terminal With Cabinet,

Get Free RF Modulator (see above)... \$499.95 plus \$10 post. Special 8" Disk Edition Explorer/85 (see above) . . . \$1499.95

- | Dius \$26 post. & insur. | Wired & Tested . . . \$1799.95 plus \$26 post. & insur. | Extra 8" CDC Floppy Drives . . . \$499.95 plus \$12 post. & insur. | Cabinet & Power Supply For Drive . . . \$69.95 plus \$3 post. & insur.

- □ Drive Cable Set-up For Two Drives . . . \$25 plus \$1.50 post. &

- ☐ Disk Controller Board With I/O Ports . . . \$199.95 plus \$2 post. & insur.

Special: Complete Business Software Pak (see above) .

\$690.06 postpaid.

SOLD SEPARATELY:

CP/M 1.4 . . . \$100 postpaid.

CP/M 2.0 . . \$150 postpaid.

Microsoft BASIC . . \$225 postpaid.

- Intel 8085 cpu User Manual . . . \$7.50 postpaid.

|   | Continental U.S.A. Credit Card Buyers Outside Connecticut | - |

|---|-----------------------------------------------------------|---|

|   | CALL TOLL FREE: 800-243-7428                              |   |

|   | To Order From Connecticut Or For Technical                |   |

| • | Assistance, call (203) 354-9375                           | _ |

|   | Iotal Engl | oseu (Comi res. ac | id stillo turt) 4   |

|---|------------|--------------------|---------------------|

|   | Paid By:   |                    |                     |

|   | ☐ Persona  | l Check 🗆 Cashie   | er's Check/Money Or |

|   | □ VISA     | ☐ Master Charg     | e (Bank No          |

| , | Acct. No.  |                    | Exp. Date           |

|   | Signature  |                    |                     |

|   | Print      |                    |                     |

| 1 | Name       |                    |                     |

|   | Address .  |                    | *                   |

|   | City       |                    |                     |

|   | 01 1       | 7in                |                     |

**NETRONICS Research & Development Ltd.** 333 Litchfield Road, New Milford, CT 06776 selects one memory block at a time, depending on the address from the CPU.

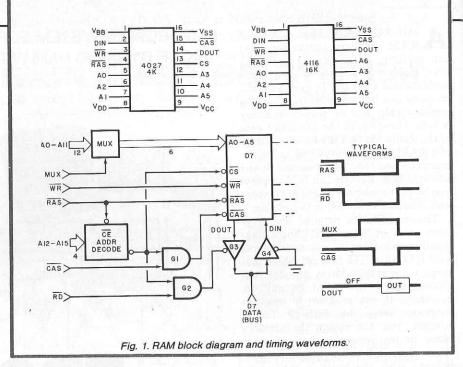

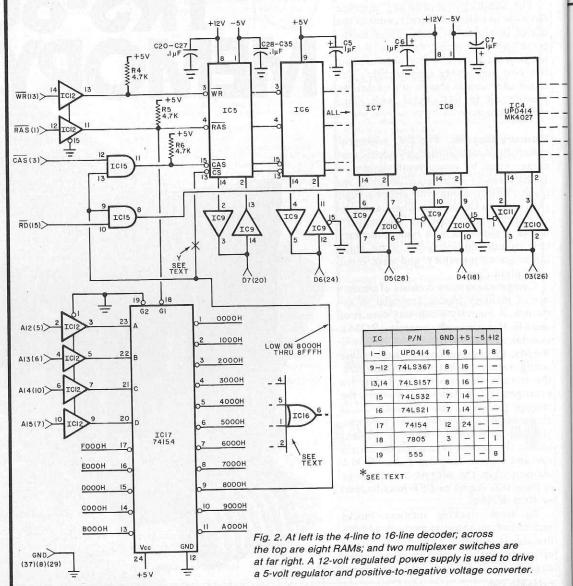

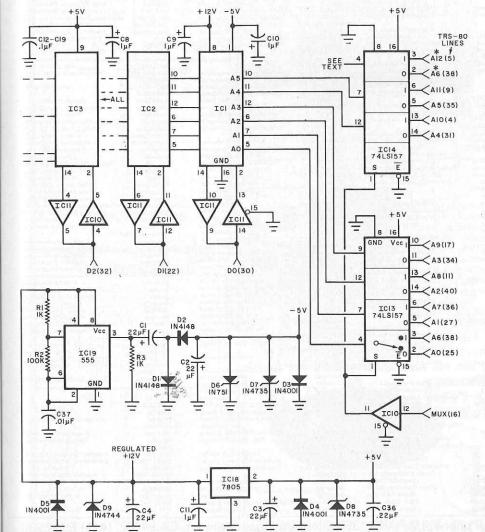

The block and timing diagram shown in Fig. 1 illustrates the operational arrangement of a 4027 4K multiplexed dynamic memory. The 4027 accepts 12 address line bits (A0 through A11) in two groups through multiplexer switches consisting of six single-pole double-throw semiconductor switches controlled by the MUX (multiplexer control) pulse. The chip data-out and data-in lines are buffered by three-state gate G3, which is controlled by gate G2 and by data-in buffer G4. The input to the address decoder consists of high-order address lines A12 through A15.

Prior to appearance of the RAS, (row address select) pulse, the address decoder is disabled and its output is high. Since gate G2 is inactive at this time, gate G3 is also off. In addition, chip select line cs is high, with memory de-

selected, gate G1 inactive, and the chip data-out line off. The MUX pulse is low and allows bits A0 through A5 to pass through the MUX switch to the chip's address input pins. On a memory read RD machine cycle, the CPU places a 16bit address on the system bus, along with MREQ and RD pulses. (Incidentally, RAS is simply a renaming of the MREQ CPU pulse.) When RAS appears, the address decoder is enabled and its decoded output goes low, enabling memory. Also, one input pin of G1 and G2 goes low, allowing read pulse RD to pass through G2 and turn on G3, but the chip is not yet ready to output data. The RAS pulse also strobes bits A0 through A5 into the chip address latches for temporary storage. The MUX pulse next appears and "throws" the multiplexer switches allowing address bits A6 through A11 to pass. Shortly thereafter, the CAS (column address strobe) pulse appears and strobes the second group of address bits into the chip.

With the full address now entered, the matrix row and column address decoders decode the address and select the stored data cell. At this point, the chip data-out line becomes active and passes the data bit to the system bus through G3. The RAS pulse goes high with chip deselection, and G3 cuts off.

Action is similar on a memory write cycle. Write pulse WR appears, G3 is off throughout the cycle, and data enters the chip through G4. MUX and CAS pulses are not supplied by the CPU; rather, they are developed by other circuit logic and properly synchronized with CPU MREQ pulse. This logic is already present in the TRS-80, and MUX and CAS pulses are on the system's bus in this and most other Z80-based systems utilizing multiplexed-address input dynamic RAMs.

For the 4116 16K version, 14 address line bits are multiplexed to the chip. To make room for two additional address line bits, pin 13 of the 4116 is used to enter bits A6 and A12, sacrificing the chip-select line. Address bits A0 and A13 enter pin 5. Then, to account for the missing chip-select line, the 4116's logic senses the proper sequence and timing of the RAS, MUX, and CAS pulses before enabling the chip.

Memory Refresh. All memory locations of the dynamic RAM must be refreshed within a 2-ms interval to avoid loss of data. This occurs on any memory cycle of a running program. It can be accomplished via software, but this reduces processing speed. Memory refresh, therefore, is best accomplished by hardware.

Refresh circuits are essentially counters that generate sequential addresses

#### **PARTS LIST**

C1 through C4—22-μF, 20-V electrolytic C5 through C11—1.0μF, 35-V tantalum electrolytic

C12 through C35—0.1-μF, 15-V disc capacitor

C36—0.22-µF, 15-V disc capacitor C37—0.01-µF, 15-V 10% disc or polystyrene

D1,D2—1N4148 switching diode D3,D4, D5—1N4001 rectifier diode D6—1N751 5.1-V zener diode D7,D8—1N4735 6.2-V zener diode D9—1N4744 15-V zener diode

IC1 through IC8—UPD414 (MK4027)\* 4K or UPD416 (MK4116)\*\* 16K RAM

IC9 through IC12—74LS367 three-state hex buffer

IC13,IC14—74LS157 quad 2-input multiplexer

IC15—74LS32 quad 2-input OR gate IC16—74LS21 dual 2-input AND gate

IC17—74154 4-to-16 line decoder IC18—7805 5-V, 1-A voltage regulator

IC19—555 timer R1 R3—1-kΩ 1/4-W 109

R1,R3—1-k $\Omega$ , <sup>1</sup>/<sub>4</sub>-W 10% resistor R2—100-k $\Omega$ , <sup>1</sup>/<sub>4</sub>-W 10% resistor

R4,R5,R6—4.7-kΩ, ¼-W 10% resistor

\*Use similar 4K RAMs on removal from TRS-80.

\*\*Use JAMECO TRS-16K kit for TRS-80 16K upgrade and for 4K to 16K board upgrade. See text.

Misc.—IC sockets; wrap posts; 20/40 card edge connector; ribbon cable; plug board; card guides; chassis; card receptacles; heat sink; 12-volt power supply (JAMECO JE210 or similar); perforated board; hookup wire; etc:

that are applied to the chips. For dynamic memory devices, it is necessary only to apply all possible row address combinations to the chip to refresh all memory locations. This RAS-only refresh is achieved in less time, and since the MUX and CAS pulses are absent, the chip is not enabled.

The Z80 CPU includes built-in refresh circuits for RAS-only refresh of the chips, this refresh occurring in the latter part of the opcode instruction fetch cycle, which is a special memory access period. Furthermore, refresh occurs while the CPU is decoding the fetched instruction, effecting hidden refresh. (For complete details, refer to the Zilog Z80 Technical Reference Manual and device specification sheets.)

Circuit Operation. Referring to Fig. 2, address decoder *IC17* is a 4-line to 16-line decoder that senses address lines A12 through A15. All decoder output lines at pins 1 through 11 and 13 through 17 are at a high logic level until RAS appears and enables the decoder through strobe line G1 at pin 18. At this time, one of the 16 output lines goes low exclusively, depending on the value of the four address input bits.

Assume that the CPU issues hexadecimal address 8000, the next address following the end of the TRS-80's resident 16K of memory. Address decoder *IC17* "sees" 8 (binary 1000) at inputs D, C, B, and A in that order. The 8000 output at pin 9 goes low and remains low through address 8FFF. On the next higher address (9000), pin 10 goes low exclusively and remains low through address 9FFF, and so forth.

Notice that, in each step, the loworder address lines run through the range of 000 through FFF (4096 addresses). Hence, the decoder can exclusively select any one of 16 4K memory blocks over the total possible 64K of memory space. However, on-chip address decoders of a selected memory block decode only the address range of 000 through FFF while depending on the external address decoder to establish block location in memory space.

Multiplexer switches IC13 and IC14 are controlled by the MUX pulse through the S control lines of the devices. Referring to the symbolic spst switch shown on IC13, all "switches" are in position 0, with MUX resting low to allow address bits A0 through A5 to pass to the RAMs. When MUX goes high, all switches move to position 1 to pass bits A6 through A11 to the chips. The multiplexers also buffer the address lines.

The memory circuit is powered by a regulated 12-volt source that in turn, powers 5-volt regulator IC18. Supplying

a small bias current to the RAMs, the —5-volt source is obtained from a charge-pump circuit formed from IC19, a 555 timer that delivers a square wave to the charge-pump circuit connected to pin 3. Regulation of the charge pump's —5-volt dc output is provided by D6, while D3, D4, and D5 provide reverse voltage protection and D7, D8, and D9 give some over-voltage protection.

RAM Kit Installation. We used a modified version of the TRS-80 disassembly instructions that are included in the computer's Technical Reference Manual to access the 4K RAMs. The procedure is as follows: With bottom screws removed and computer in its normal operating position, remove the top to reveal the keyboard. Next, hinge the keyboard to a vertical position, taking care to avoid strain on the short ribbon cable, and remove the five rubber spacers to free the main board. Lower the keyboard to the table top and rest it on its keytops. In a similar manner, hinge the main board outward and place it on the inverted keyboard. Reverse the procedure to reassemble.

We used the Jameco TRS-16K RAM kit which contains eight UPD416 (MK4116) high-speed RAMs and instructions for installation. Since the chips are easily damaged by static electricity, we recommend that you connect an earth ground wire to the main board circuit, and connect yourself to earth ground through a 250,000-ohm resistor.

and a wire running to a metallic wristwatch strap. Stay clear of ac lines and equipment! Use a dot of fast-drying white paint to mark the pin-1 position of each DIP shunt and 4K RAM socket location.

Remove the somewhat fragile DIP shunts, and replace with substitutes, such as 16-pin DIP headers, jumper wired according to instructions supplied. The DIP shunts and RAMs extract with difficulty, so go easy. As you remove each RAM, push it into black conductive foam plastic. Then install the 16K RAMs, being sure to orient them properly in their sockets.

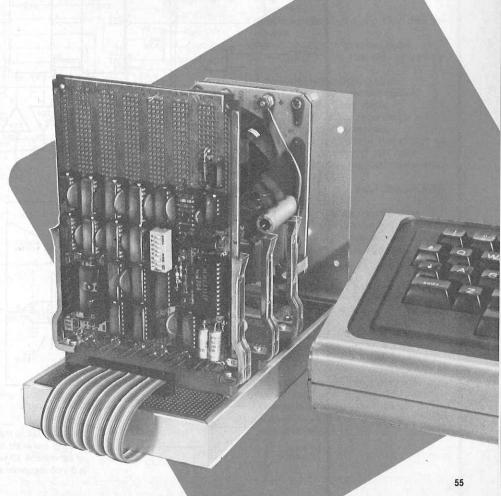

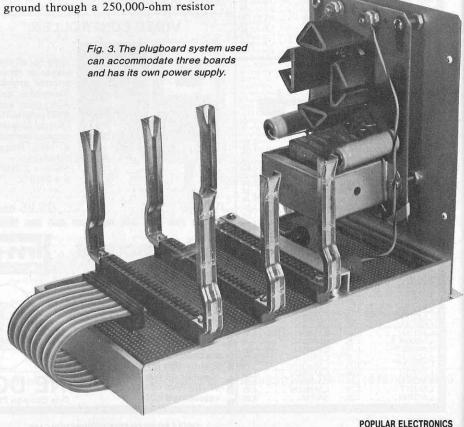

If you don't have a similar system, you can assemble the plug-board system shown in Fig. 3 as follows: Install three Vector No. R644-3 44-contact receptacles on 41/2" × 6" perforated board drilled as required. Bolt Vector No. BR27D card guides and receptacles to the board and slide the Wire-Wrapped assembly into the 51X-1 aluminum frame. The memory board operates off a regulated 12-volt power supply, which can be mounted on a vertical plate bolted to the frame as shown. (If you aren't planning to use a plug-board system at this time, assemble the circuit on a Vector No. 8802 Circbord that has etched buses on one side of the board, and slide the board horizontally into the aluminum frame.)

Use only a short ribbon cable to interconnect the computer and expansion system. Connect a 6" length of 40-conductor ribbon cable to a TRS-80 card edge connector. For reduced crosstalk, overlay one side of the cable with aluminum foil. Then connect bare wire pigtails to the connector's ground lugs and tape the pigtails to the foil. Omit any

If you prefer a disconnect at the plugboard system, cut a preassembled 40conductor female IDC ribbon cable to length and solder to the edge connector. Install two rows of No. T46-5-9 wrap posts into the perforated board with pin faces in square alignment to accept the female IDC plug.

connection to TRS-80 5-volt line 39.

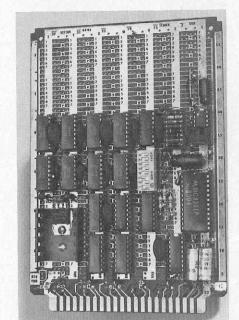

The plug board shown is a Vector No. 4494 44-contact board with etched ground and supply planes on opposite sides. Assign the +12-volt supply to one of the spare bus lines. Install the sockets for the multiplexer and buffer ICs in the first two socket tiers near the card fingers and install the RAM sockets in the third and fourth socket tiers. This leaves ample room for another bank of eight memory devices. Do *not* install the ICs in their sockets until told to do so!

Charge-pump components can be installed on a DIP header and plugged into a single socket as shown. Install small bypass capacitors with minimum lead lengths. (In the prototype, some bypass capacitors were connected directly to socket-wrap posts.) The board is preferably chain-wrapped using the Vector No. P180 Slit-N-Wrap or similar tool. To keep crosstalk low, avoid bundling the wires.

When 20K of RAM isn't enough, you can easily install 16K RAMs on the expansion board to obtain a total of 32K of memory. To do this, first break the wire at point Y (see Fig. 2) to RAM pin line 13. Remove address line A6 from pin 3 of IC13 and connect address line A13 to pin 3 of IC13. Wire lines A6 and A12 to IC14 as shown, and connect pin 4 of IC14 to RAM pin line 13. Remove the connection from pin 9 of IC17 and wire it to pin 6 of IC16. Assuming there is 16K of RAM inside the TRS-80, connect the four input pins of active-low OR gate IC16 to pins 9, 10, 11, and 13 of IC17 in any order.

After checking your wiring for errors and shorts, install only IC19, apply power, and check that the proper supply voltages appear at the appropriate socket pins. Disconnect power. Then install the remaining ICs, taking precautions with the MOS RAMs.

**Checkout.** You can check the 16K of RAM installed in the TRS-80 by running the "Function and RAM test" pro-

#### CKMEM PROGRAM

| ADDR | CODE     | MNEMONIC     | REMARK                    |

|------|----------|--------------|---------------------------|

| 4400 | 21 18 44 | LD HL, 4418H | ; INITIALIZE POINTER      |

| 4403 | 0E 01    | LD C, 01H    | ; TEST PATTERN BUFFER     |

| 4405 | 71       | LD (HL), C   | ; WRITE PATTERN IN LOC.   |

| 4406 | 06 08    | LD B, 08H    | ; SET LOOP COUNT TO EIGHT |

| 4408 | CB 06    | RLC, (HL)    | ; ROTATE LEFT CIR. IN MEM |

| 440A | CB 01    | RLC, C       | ; AND IN REGISTER C       |

| 440C | 79       | LD A,C       | ; GET TEST PATTERN AND    |

| 440D | BE       | CP (HL)      | ; COMPARE                 |

| 440E | 20 05    | JRNZ, 5      | ; EXIT ON MEM ERROR       |

| 4410 | 10 F6    | DJNZ, - 10   | ; ELSE LOOP TILL DONE     |

| 4412 | 23       | INC HL       | ; POINT TO NEXT MEM LOC.  |

| 4413 | 18 F0    | JR, -16      | ; LOOP TO CONTINUE TEST   |

| 4415 | CD 91 40 | CALL, 4091H  | ; STOP IN TBUG            |

|      |          |              |                           |

grams listed in the TRS-80 User's Manual. Running time is about 12 minutes. Next, with the power disconnected from both the TRS-80 and expansion module, connect the two together. Power-up first energizing the expansion system and then the computer. On typing the command PRINT MEMORY, 19,967 should appear on-screen. If not, deenergize the TRS-80 for 10 seconds and try again. If

The memory expansion system mounted on a 4494 plug board. There is room for eight additional RAMS if desired.

the computer still won't function properly, power down and check for bus line shorts. (If the program prints out RAM error immediately, look for wiring errors.) If the test program runs well into the test but stops at random times, the most likely cause is noise or crosstalk. A short ribbon cable, low-impedance ground and supply lines, and adequate bypassing are required.

Users of the TRS-80 TBUG machine-language monitor have the option of placing the 4K of RAM at the far end of memory. This obviates the need to

revise machine language programs located at the far end of memory when you add more memory. A DIP switch can be used to select either pin 9 or pin 17 of IC17, allowing instant movement of the 4K block to the far end of memory. On powering up when using memory beginning at F000 always energize the TRS-80 first. Typing PRINT MEMORY should now yield 15,871 on-screen.

With any use of the RESET button, always type in PRINT MEMORY. For rapid memory checks and troubleshooting, use machine language program check memory CKMEM, which runs through 20K of memory in 5 seconds. You may wish to acquire the TBUG monitor for high-speed memory tests if for no other reason than to run CKMEM.

Check Memory Program. The CKMEM program given in the table writes a test pattern of a single 1 bit into a memory location and reads back the stored pattern for a comparison test. Rotated left circularly, this 1 bit is used to check all bit positions. Whenever a mismatch or RAM error is encountered, the program exits to TBUG monitor control and register pair HL holds the address at mismatch.

Entered as listed in Level I machines, the CKMEM program begins testing at address 4418 as shown in the first instruction. No changes are required to relocate the program in memory, apart from starting address initialization. The program can be used to fill memory with 0s by changing the second instruction to 0E 00. To check 4K of RAM at the remote end of memory, change the first instruction to 21 00 F0.

Program CKMEM may miss certain address-line wiring errors of the RAM board that are caught by the TRS-80 RAM test program. Either program will catch bad chips. Program CKMEM and TBUG monitor commands simplify isolation of a bad RAM, but don't be too quick to condemn a chip until it is proven defective by direct substitution. Once the whole system is up and running, you are ready to broaden your programming horizons with a system that has enough RAM to run sophisticated software.