# Popular Electronics

WORLD'S LARGEST SELLING ELECTRONICS MAGAZINE

**JANUARY 1982/\$1**

## HOW TO ADD

- Safe, Convenient Shutoff to Smoke Detectors

- "Real World" Signal Handling to TRS-80 Computers

- Overseas Broadcast Reception to Any AM Radio

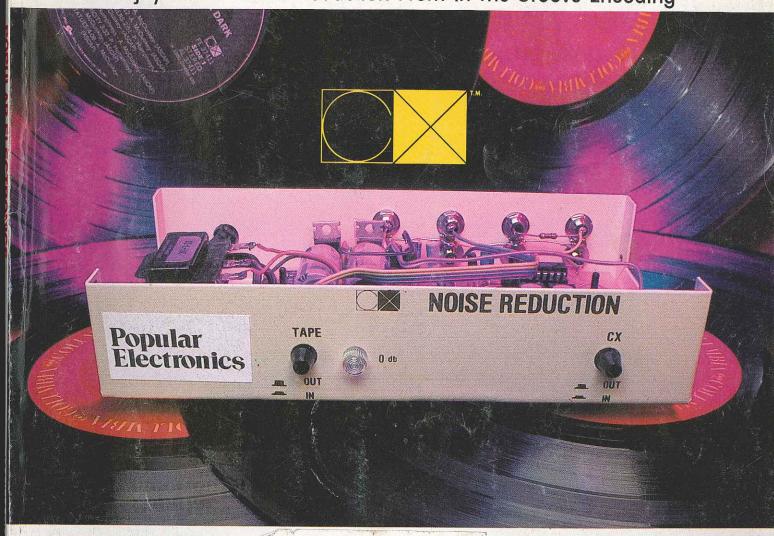

# \$70 Decoder for New Records

Enjoy 20-dB Noise Reduction From In-The-Groove Encoding

# ANALOG-DIGITAL CONVERTER

FOR TRS-80 INTERFACING

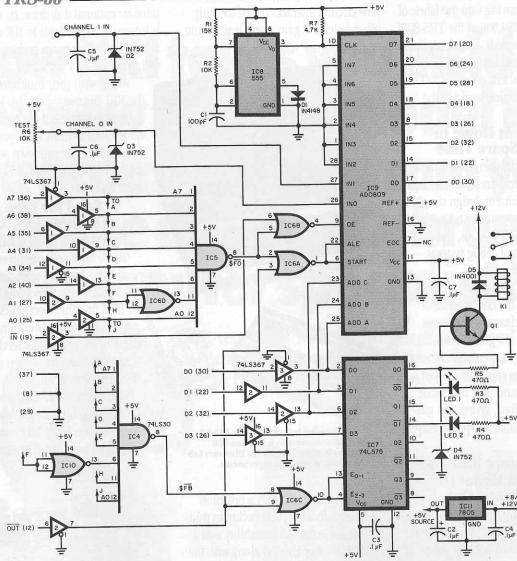

An 8-bit, 8-channel digital circuit that allows you to connect analog voltages to your TRS-80 microcomputer

DIGITAL computers "speak and understand" only the binary language of electrical ones and zeros. Unfortunately, the binary language is not suitable for direct measuring of physical quantities such as voltage, pressure, temperature, light, or other continuously varying (analog) parameters. To utilize the digital computer in measurement and control systems, an analog-todigital interface is required. Fortunately, such analog-to-digital converters (ADC) are now available at low cost.

Interfacing with the TRS-80 Model I microcomputer, the 8-bit, 8-channel ADC covered in this article includes a four-bit output port for controlling lamps, relays, and other devices. The output port is readily expandable to eight channels, thus providing 32 channels of control. Running in the TRS-80 TBUG monitor, the accompanying machine language program ANADIG shows how to structure a multichannel data-acquisition system. Several input and output circuits are detailed, including means to quantize the range of an input channel to output multiple decisions controlling a number of output circuit branches. The ADC accepts an input voltage and converts it to binary form for display or further processing by a computer. Common converter types include the costly high-speed 'flash' converter, the inexpensive but slow ramp converter, and the successive-approximation converter that provides excellent speed at relatively low cost. In all cases, the ADC seeks to match the level of an analog input signal with stepped and weighted reference voltages and generate a binary value when the match is

Considering first the successive ap-

proximation converter, Table I shows conversion of input signal of weight 67 in eight approximations taken in sequence. On the first comparison (bit D7), weight 128 is greater than 67 thus it is discarded by setting output bit D7 to zero. On trial two, weight 64 is less than 67 and is retained as a partial sum by setting bit D6 to one. The following comparisons through bit D2 are discarded because the partial sum would exceed 67. The remaining two trials bring the sum to exactly 67 and the corresponding data bits are set to one causing 67 to be converted to 01000011 or 43 hex. For an input signal of weight 255, the data bits are set to 11111111 yielding FF hex or full-scale. The converter resolves full-scale input of one part in

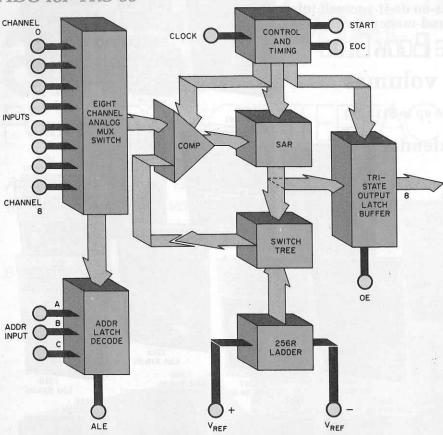

The block diagram of Fig. 1 shows the internal circuit blocks of the eight-chan-

POPULAR ELECTRONICS

Into electronics, amateur radio, or computers?

Looking for exciting projects, troubleshooting and repair tips, or hands-on do-it-yourself info? Find hundreds of time-and-money-saving ideas in the ELECTRONICS BOOK CLUB

Select 6 exceptional volumes

for only \$295 (total value up to \$113.70)

1982 Electronics Projects Calendar FREE!

### 7 very good reasons to try **Electronics Book Club** Blue Ridge Summit, PA 17214

Publisher's List \$5.95

· Reduced Member Prices. Save up to 75% on books sure to

increase your know-how · Satisfaction Guaranteed. All books returnable within 10

days' without obligation • Club News Bulletins. All about current selections—mains,

alternates, extras—plus bonus offers. Comes 14 times a year with dozens of up-to-the-minute titles you can pick from · "Automatic Order". Do nothing, and the Main selection will be shipped automatically! But . . . if you want an Alternate selection—or no books at all—we'll follow the instructions you give on the reply form provided with every News

· Continuing Benefits. Get a Dividend Certificate with every book purchased after fulfilling membership obligation, and qualify for discounts on many other volumes

· Bonus Specials. Take advantage of sales, events, and added-value promotions

• Exceptional Quality. All books are first-rate publisher's

editions, filled with useful, up-to-the-minute info

## ELECTRONICS BOOK CLUB Blue Ridge Summit, PA 17214

Please accept my membership in Electronics Book Club and send the 6 volumes circled below, plus a free copy of the 1982 Electronics Projects Calendar I understand the cost of the books selected is \$2.95 (plus shipping/handling). If not satisfied, I may return the books within ten days without obligation and have my membership cancelled. I agree to purchase 4 or more books at reduced Club prices during the. next 12 months, and may resign any time thereafter.

1062 1066 1070 1076 1097 1108 1128 1136 1218 1225 1229 1230 1233 1245 1249 1250 1251

| NamePhor                                                  |                   |  |

|-----------------------------------------------------------|-------------------|--|

| Address                                                   | tilling knings an |  |

| City                                                      |                   |  |

| State                                                     | Zip               |  |

| (Valid for new members only, Foreign and Ganada add 20%.) | PE-1              |  |

Fig. 1. Block diagram of the circuits contained in the AD0809 analog-to-digital converter used in the project.

nel converter used in this project. One of eight input signals is applied to one input of the comparator through a mux (multiplex) analog switch. The particular channel selected depends on the address bits applied to the address data latch decoder. Bit 000 selects input channel 0, bit 001 selects channel 1, and so forth up to channel 7 by bit 111.

A stable 5-volt reference is applied to a 256R resistor ladder network that supplies weighted reference voltages for comparisons. With the input signal present at one input of the comparator, a switch tree sequentially selects and applies weighted reference voltages to the other comparator input. The comparator output feeds into the successive approximation register (SAR) which performs logical decisions and assembles the binary output data in the Tri-State data-out latch and buffer. The ADC clock and timing and control circuits determine the sequence of events. Using this arrangement, at a clock frequency of 640 kHz, conversion takes place in 116 microseconds.

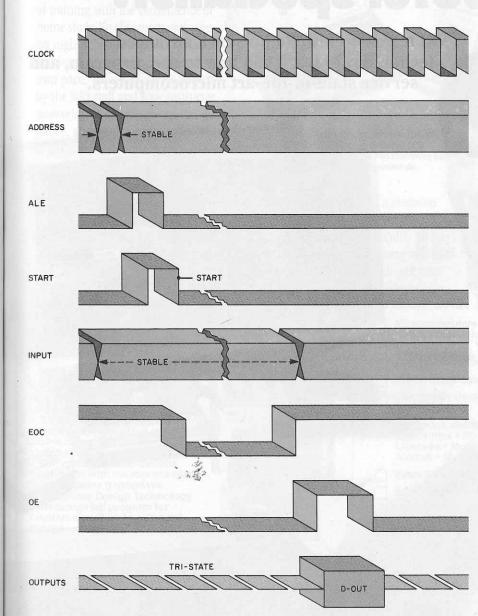

Figure 2 shows the ADC timing. With address bits and input signal present, address latch enable pulse (ALE) strobes the address bits into the address latch decode circuit. Pulse START initiates conversion and end-of-conversion pulse (EOC) goes low during conversion.

Following conversion, pulse EOC goes high and pulse output enable (OE) is applied to enable the data onto the bus for acceptance by the computer.

For comparison, a six-bit parallel flash converter includes a resistor ladder supplying 63 reference voltages each connected to one input of 63 comparators. The input signal connects to the

### Table I **EXAMPLE OF SUCCESSIVE APPROXIMATION**

|   | Bit | Weight | Comparison | Bit 3 | sum |   |

|---|-----|--------|------------|-------|-----|---|

|   | D7  | 128    | 128>67     | 0     | 0   |   |

|   | D6  | 64     | 64<67      | 1     | 64  |   |

|   | D5  | 32     | 32+64>67   | 0     | 64  |   |

|   | D4  | 16     | 16+64>67   | 0     | 64  |   |

|   | DЗ  | 8      | 8+64>67    | 0     | 64  |   |

|   | D2  | 4      | 4+64>67    | 0     | 64  |   |

|   | D1  | 2      | 2+64<67    | 1     | 66  |   |

|   | DO  | 1      | 1+66=67    | 1     | 67  |   |

| 1 |     |        |            |       |     | 1 |

other input of all comparators. Comparisons take place all at once thus the name "flash" converter. The 63 outputs of the comparator string are then decoded by extensive and complex logic to form the equivalent binary output. However, an eight-bit flash converter requires 255 comparators! Costly to manufacture, the flash converter is usually limited to six bits or less.

The ramp ADC technique uses a digital-to-analog converter (DAC) and a computer program to generate a staircase voltage ramp of 256 steps for use by the eight-bit converter. The stepped output of the DAC and the input signal connect to comparator inputs, and on each successive voltage step, the computer program checks comparator output and advances to the next step if the match is not found. Two hundred and fifty-five comparisons are required to reach full-scale for eight-bit conversions. Though relatively slow, ramp-conversion techniques offer advantages through software control.

Circuit Operation. As shown in the schematic of Fig. 3, clock generator IC8 is a 555 timer operating at approximately 100 kHz. Input channels 0 and 1 are the only ones used at this time, with the remaining 6 input channels grounded. A zener diode (D2, D3) and a capacitor (C5, C6) protect the active CMOS input channels.

When the program ANADIG issues an OUT instruction to port address FD (decoded by IC5), the instruction transmits channel address bits on data lines D0, D1, and D2. Thus IC5 in conjunction with the OUT signal activates IC6A pulsing ALE and START inputs with the address latched into the ADC. A time delay in the program allows time for completion of the conversion. The program then issues an IN instruction to port address FD causing IC6B to activate OF (output enable) and placing the converted data on the data bus as input to the computer.

A program task subroutine then processes the data and makes a decision for use by output port, IC7. The task decision is output to port address FB decoded by gate IC4 and enabling IC7. Data bits D0 through D3 are transmitted to IC7 and determine the output of four data latches used to control external indicator lamps or relays.

In the case of an external transistor driver (Q1), zener diode D4 protects the circuit in the event of failure of the transistor. Voltage regulator IC11 supplies five volts to the circuit.

Additional input channels may be connected to IC9 as required. Additional output channels are created by adding another 74LS75 (IC7) and connecting

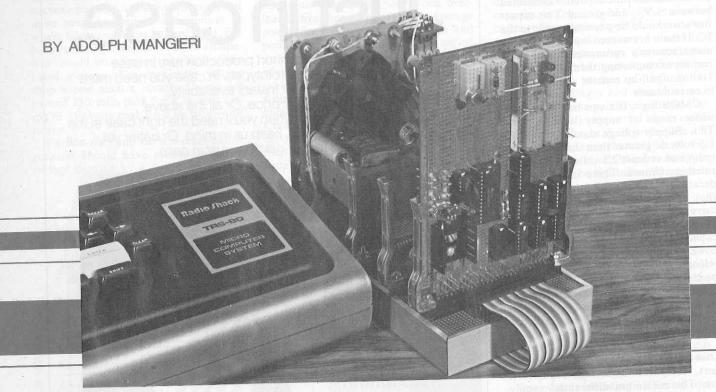

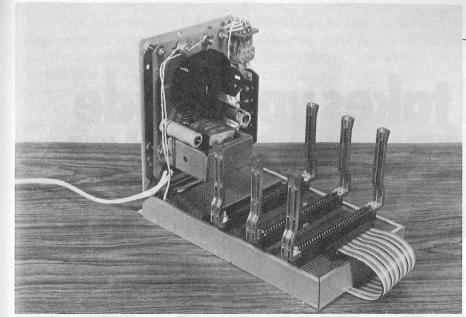

The system is assembled on an aluminum frame with power supply and card guides.

Fig. 2. Timing diagram of the analog-to-digital converter IC.

device pins 4 and 13 to pin 10 of IC6C. Data lines D4 through D7 are passed through the spare buffers of IC3 to the inputs of the second data latch.

Construction. The circuit was assembled on a Vector 4494 ANY-DIP plug card and wire wrapped. Install IC1, IC2. IC3, and IC10 in the socket row near the card fingers. Install IC4, IC5, and IC6 in the second socket row and place IC7, IC8, and IC9 in the third row. Experimentation with assorted input and output circuits can be facilitated by installing pairs of Vector T66-96 and T66-32 Klip Bloks and two T45-24 Klip Buses on the upper portion of the card as shown. The plug-board system shown consists of three Vector R644-3 44-contact card receptacles and three pairs of BR27D card guides installed on the 51X aluminum frame. Install two rows of T46-5-9 board pins with pin faces aligned on perfboard at one end forming a male IDC connector. Use a 40-line IDC cable disconnect at the plug board system. A Jameco No. JE210 5-to-15volt adjustable regulated power supply set for 12-volts powers the circuit. Do not run the TRS-80 5-volt supply to the plug board system. As an alternative to the plug board system, assemble the circuit on Vector 8002 or 8004 Circbords for wire wrapping and install the card in the 51X aluminum frame.

Checkout. With integrated circuits removed and ribbon cable disconnected from the computer, power the voltage regulator and check voltage distribution at the pertinent socket pins. Check voltages at the far end of the cable and be certain that supply voltages do not feed back to the computer. Install the integrated circuits taking usual precautions when handling the CMOS converter chip. Energize the circuit and verify presence of clock pulses at pin 3 of IC8 using either a counter or oscilloscope. With power off, make connections to the computer and verify proper operation of the computer. Look for shorted bus lines if the computer fails to function.

Connect the input test circuit shown on the schematic diagram to the input of channel zero. Jumper channel-one input to channel-zero input. Enter and load program ANADIG into memory using the TRS-80 T-BUG monitor and break the looping program by inserting STOP code CD 91 40 at address 4A27H. Set test potentiometer R6 to its ground end, and run the program. Both LED1 and LED2 should turn off. Verify that data input buffer memory location 4A00H and 4A01H hold data 00 and that outport buffer 4A08H holds 00. Set the test potentiometer to five volts and observe that both LEDs glow. Verify that chan-

JANUARY 1982

Fig. 3. A 555 clock generator, IC8, operates at approximately 100 kHz. Input channels 0 and 1 are the only ones used in this application.

#### **PARTS LIST**

IC9-ADC 0809 eight-bit, eight-channe

IC11-7805 5-V, 1-A voltage regulator

LED1,LED2-Light-emitting diode (XC-

Q1-2N3053, RS-276-2030 npn transistor

ADC (available from Jameco Electronics,

1355 Shoreway Rd., Belmont, CA

IC7-74LS75 4-bit data latch

IC8-555 time

94002)

K1-12-V relay

526R or equiv.)

R1-15-kΩ,1/4-W resistor

C1-100-pF ceramic capacitor C2-1.0-µF, 35-V tantalum electrolytic C3 through C7-0.1-µF, 15-V disc capaci-D1-1N4148 switching diode D2,D3,D4-1N752 5.6-V zener diode D5-1N4001 rectifier IC1.IC2.IC3-74LS367 three-state hex IC4,IC5-74LS30 8-input NAND gate IC6,IC10-74LS02 quad 2-input NOR

nels zero and one data buffers hold data

FF or 255 while outport buffer 4A08H

now holds 03. Vary R6 slowly about the

trip points. Notice that LED1 flickers

and relay K1 chatters at the trip point.

Notice that the turn-on and turn-off

points of LED2 differ slightly and with

no flicker. This is the result of dead-

band or hysteresis built into the task

Software. Use program ANADIG shown here for initial experiments with multichannel data acquisition and processing and write your own programs for specific applications. The looping main program RUN performs initializations, issues channel addresses, and CALLs subroutine START which initiates A/D conversions followed by subroutines TASKO and TASK1 which control the

R2-10-kΩ, 1/4-W resistor R3.R4.R5-470-Ω, 1/4-W resistor R6-10-k $\Omega$  potentiometer R7-4.7kΩ, 1/4-W resistor

Misc: Vector 4494 plug board; 51X aluminum frame; R644-3 44-contact card receptacles (3); BR27D card guides (6); T46-5-9 board pins; perfboard; 28-pin DIP socket: 16-pin DIP sockets (4); 14pin DIP sockets (4); T49 Klip-Wrap posts; T66-96, T66-32 Klip Bloks (pairs); T45-24 Klip Bus (2); ribbon cable and connectors; wire; etc.

relay outport. Memory locations 4A00H

through 4A07H respectively store input data for channels zero through seven. Location 4A08H holds the outport byte common to all output channels. Tracing through a typical program run, index register IX is initialized to point to the input data buffer. The outport byte is arbitrarily cleared to 00. Channel zero address 00 is first loaded

**ANADIG TEST PROGRAM** OOLOO : FILENAME - ANADIG OOLLO ; BY ADOLPH A. MANGIERI 4/81 OO120 ; CHAN BUFFER - LAOOH THRU LAO7H 00130 ;OUTPORT BUFFER - LAOSH 00170 00150 DEFS BUFFERS 4A09 DD21004A 00160 RUN LD IX . LAOOH POINTER (IX /8H), OOH CLR BUFFER LAOD DD360800 00170 00180 LOOP1 LD CHAN O HOO.A START START A/D 00190 4A16 DD7700 (IX/O),A SAVE DATA 00200 00210 CALL TASKO DO TASK O A,OLH CALL START A/D 00230 START LD (IX/1),A SAVE DATA 00250 CALL DO TASK 1 00260 JR LOOP1 LOOP DEFS SPACE 00270 00280 START PUSH SAVE 00290 (OFDH),A START A/D 00300 B,2FH TIME DELAY 00310 LOOP2 DJNZ LOOP2 :LOOP2 GET DATA 00320 TN A, (OFDH) 00330 POP RESTORE RET RETURN AF HL DE SPACE 00350 DEES 00360 TASKO PUSH SAVE 00370 PUSH SAVE SAVE PUSH LD H,OOH CLEAR H 00390 ID CLEAR D D. OOH 00/100 L,7CH TRIP POINT 001,10 OR LD CLEAR CARRY 00/120 E,(IX/0) GET DATA 00/130 SBC COMPUTE HL.DE :GO IF NEG

LASF DS LIAAO 2600 LAA2 1600 LAAL 2E7C 4AA6 B7 LAAT DDSROO LAAA ED52 LAAC FABSLA 00450 JP RES M.SETO LAAF DDCB0886 OOL60 0,(IX/8) JR LAB3 1804 00L70 LDPORT LABS DDCBO8C6 OOL80 SETO SET 0,(IX/8H LAB9 DD7E08 00490 LDPORT LD A, (IX/8H OUT 00500 (OFBH),A LABC D3FB POP 00510 LARE DI 00520 LABF E1 00530 POP AF LACO F1 00540 RET 4AC1 C9 00550 DEFS 25 AF 0019 00560 TASK1 LADB F5 PUSH LADO E5 LADD D5 00570 PUSH HL DE 00580 PUSH LD LADE 2600 00590 H, OOH ID ID ID ID 00600 D, OOH JIABO 1600 L,7EH 00610 LAB2 2E7E LABL DDSEO1 00620 OR 4AB7 B7 00630 LAES ED52 00640 SBC HL,DE JP LD m,šeti 00650 00660 L,7AH 00670 SBC HL, DE JP P.RES1 EXIT 00690 SET 00710

00هيا

LA11 3E00

LA13 CD7ALA

LA19 CD9DLA

LAIC 3EOL

LAIR CD7ALA

4A21 DD7701

LAZL CDDBLA

4A27 18E8

LATE D3FD

4A7D 062F

LATE 10FE

LAS1 DBFD

4A83 C1

4A84 C9

449D F5

LASE E5

0018

0051

LATA C5

0009

; COMPUTE ;SET BIT 1 : LO LIMIT : COMPUTE :JP IF POS ; TO EXIT 1,(IX/8H) ; SET BIT 1 RES BIT 1 RES LD :GET DATA A,(IX/8H SEND DATA OUT (OFBH),A RESTORE POP DE HL AF RESTORE POP RESTORE POP RETURN RET END

RES BIT O

SET BIT O

GET DATA

SEND DATA

RESTORE

RESTORE

RESTORE

RETURN

;SPACE

: SAVE

:SAVE

: SAVE

CLEAR H

;CLEAR D

;HI LIMIT

GET DATA

:CLEAR CARRY

EXIT

цава Гагоца LAED 2E7A LAEF ED52 LAFI F2FCLA LAF4 180F LAF6 DDCBO8CE 00700 SET1 4AFA 1804 LAFC DDCB088E 00720 RES1 4B00 DD7E08 00730 OUTPRT 4B03 D3FB 4B05 D1 00750 EXIT 4B06 E1 00760 4B07 F1 00770 4B08 C9 00780 0000 00790 0000 TOTAL ERRORS OUTPRT 4B00 LBO5 LAFC LAF6 EXIT RES1 SET1 LDPORT **4AB9** SETO LAB5 4A7F LOOP2 LADB TASK1 LA9D TASKO LA7A START 1.477 LOOP1 LA09

into register A and subroutine START is CALLed. Routine START loads the address into the converter and starts A/D conversion. After a time delay set by byte 2F at address 4A7EH, the program returns to RUN with converted data in register A. Program RUN stores the data at address 4A00H and CALLS TASKO. Subroutine TASKO fetches the stored input data and subtracts it from trip point 7C (124) located at address 4AA5H. If the result is negative, bit B0 of the outport byte is set to one or otherwise set to zero. The outport byte is then transmitted to the relay port data latch. Bit B0 now as data bit D0 may alter the status of output channel zero. The next program module of RUN addresses itself to channel one and TASK1 in a similar

Subroutine TASK1 includes an upper trip point 7E (126) at address 4AE3H and a lower trip point 7A at address 4AEEH. When the converted input falls between these limits, bit B1 of the outport data byte is left unchanged. This introduces hysteresis much like a Schmitt trigger and prevents repetitive operation of mechanical relays and solenoids when the input levels hover near the trip points. The trip points and deadband are readily altered to suit the application. Use the TRS-80 TBUG machine language monitor to enter the object code. No changes are required for entry into either Level I or Level II machines. Alternatively, enter the source code or assembly listings using TRS-80 Editor/Assembler EDTASM. Once the code is entered, make a tape copy using TBUG. Minor program changes are best entered manually using the TBUG. For major alterations, restructuring, or relocation of code, use EDTASM which markedly reduces the effort.

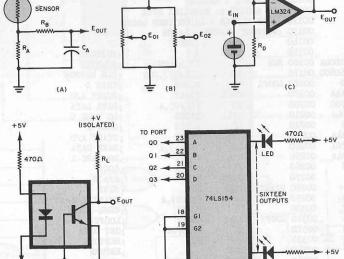

Input and Output Circuits. Input circuit Fig. 4A uses a thermistor for sensing temperature or a light-dependent resistor for sensing light levels. Resistor Ra can be a potentiometer for calibration or setting of trip points. The sensor and pot can be interchanged. It is best to include RC filtering in the input circuit to remove noise and ac components which affect conversion. Try 100,000 ohms for Rb and 0.1 µF for Ca or higher values if the RC time constant is not objectionable. Figure 4B shows two potentiometers of a joystick having two outputs which feed into two channels of the ADC, with the game program processing the converted data.

Low-level voltages from devices such as a photovoltaic cell or thermocouple can be amplified by an op amp such as the LM324 as shown in Fig. 4C. Stage gain or scaling depends on the ratio of

RUN

ADC for TRS-80

Fig. 4. Inputs: (A) a thermistor or light sensor; (B) two outputs of a joystick; (C) an amplifier to step up low-level signals. An optoisolator (D) is used to drive a triac or SCR. A decoder can be used on the output (E) to drive a display or LED or an alarm.

resistors Rc and Rd. For scaling, use a potentiometer for Rc. Higher input voltages can be scaled using a voltage divider string. For low-voltage ranges, scaling is obtained by switching suitable values of resistor Rc. If you use 2.55-volts dc for the ADC reference voltage, full-scale or 255 occurs with an input voltage of 2.55 volts. For video display of converted data, include a subroutine which converts binary to ASCII for display in video memory space. This and other useful subroutines such as multiplication and division can be found in manuals on Assembly language programming.

Output circuits include indicator lamps, audible alarms, mechanical and solid-state relays, stepping motors, and similar devices. Mechanical relays provide electrical isolation between the computer circuits and the controlled power circuits. Where triacs or SCRs are used to control power, use an optoisolator as shown in Fig. 4D. Alternatively, install a reed relay on the plug board for control of solid-state or re-

mote-mounted mechanical relays.

Through program subroutines, the full-scale range of the ADC input can be divided into a number of segments each issuing a unique decision to the outport. As an example, the task program can divide full-scale range into sixteen segments with each program segment issuing a unique 4-bit nyble ranging from 0000 to 1111. The nyble is output to the 74LS75 latching port and affects the four outputs.

As shown in Fig. 4E, a 4-to-16-line decoder is connected to the Q outputs and decoded to one of sixteen outputs. The output lines can activate an array of sixteen LEDs arranged as a bar graph (for example), or to activate audible alarms or process controls.

The ADC and the DAC open the door to interfacing the computer with practical tasks in the home and in industry. At far less than the cost of available interfaces, you can begin experimenting with the ADC and put your own ideas to use at home.

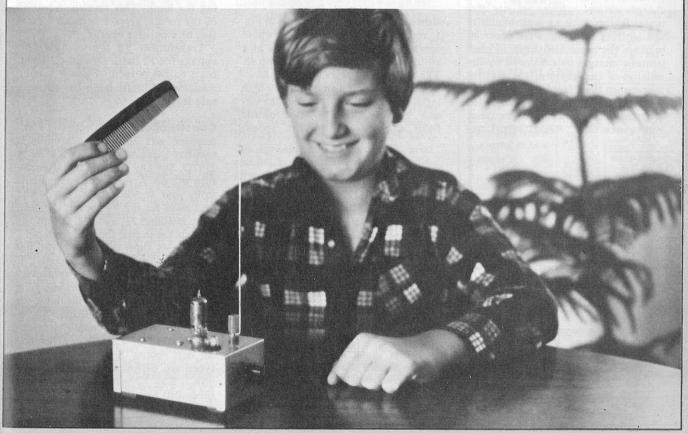

"Harold and I are so proud, Mother. Baby encoded his first word today!" A Science Fair Project for Your Youngster:

# THE ELECTRONIC ELECTROSCOPE

Indicates when strong electrostatic field exists

#### BY KEITH KUNDE

PRIOR to 1792 and Allesandro Volta's development of the chemical battery, nearly all electrical experimentation and research involved static electricity. Such static charges are generated on many nonconducting materials through friction with a complementary material, with combinations such as glass and silk, sealing wax and wool, and solidified sulfur rubbed by hand, leading the way in early experiments. Of course, the early experimenters had no means for directly measuring their static

charges, but they did observe the forces of attraction and repulsion produced by charged objects. These observations led to the introduction late in the 16th century of the earliest form of electroscope by William Gilbert, who used a pivoting metal pointer to demonstrate the presence of static charges.

Another early form of electroscope used small balls of pith or cork suspended by fine insulating threads so that the forces of attraction and repulsion could be observed through the motions of the charged balls. In 1787, Abraham Bennet invented what became the most familiar form of the device—The Gold-Leaf Electroscope, which consisted of a small brass box having glass windows on two opposing sides, inside of which two strips of very thin gold leaf were suspended face-to-face from a metal rod. The rod passed through a cork in the top of the box and was terminated with a brass disk on its outer end.

A charged object near the disk would cause a similar charge to be

SEND FOR FREE 200 PAGE AUDIO/VIDEO GATALOG CIRCLE NO. 28 ON FREE INFORMATION CARD

POPULAR ELECTRONICS JAI